Bootstrap specific – AMD Geode LX [email protected] User Manual

Page 554

554

AMD Geode™ LX Processors Data Book

GeodeLink™ Control Processor Register Descriptions

33234H

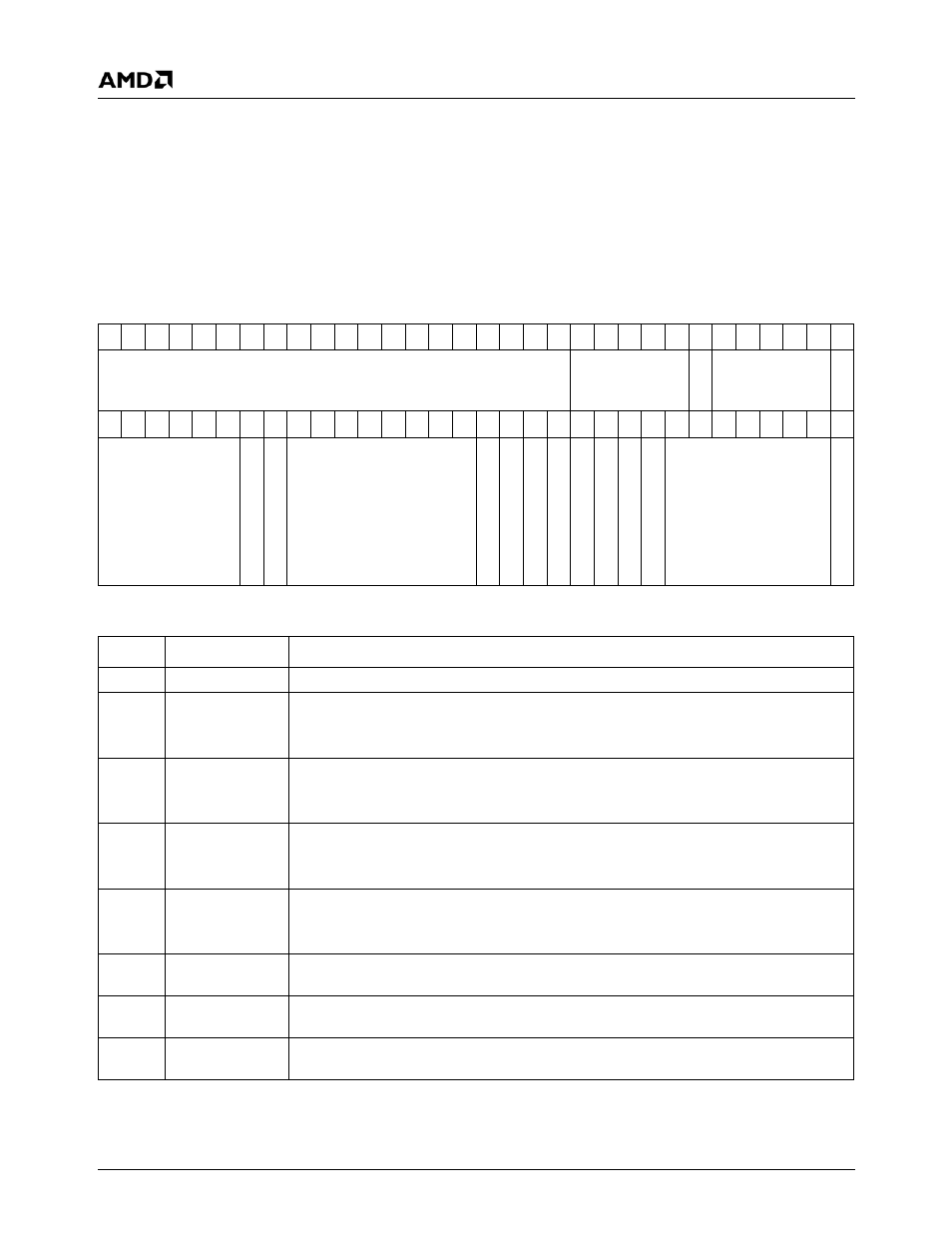

6.14.2.13 GLCP System Reset and PLL Control (GLCP_SYS_RSTPLL)

This register is initialized during POR, but otherwise is not itself reset by any “soft-reset” features. Note that writing this reg-

ister always has immediate effect, so read-modify-writes must be done to avoid corrupting the PLL timing settings. When

using this register functionally to change PLL frequencies, the CHIP_RESET bit (bit 0) should be set. Writing this register

with the CHIP_RESET bit set will never send a write-response over the GLIU (this allows halting bus traffic before the reset

occurs).

MSR Address

4C000014h

Type

R/W

Reset Value

Bootstrap specific

GLCP_SYS_RSTPLL Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

GLIUMULT

MBDIV

COREMULT

COR

E

DIV

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

SWFLAGS

GLIULOCK

CORELOCK

HOLD_COUNT

RSVD

GLIUPD

COREPD

GLIUBYP

A

S

S

COREBYP

A

S

S

LPF

E

N

V

A

_

S

EM

I_

SY

N

C

_

M

O

D

E

PCI_SEMI_SYNC_MODE

BOOTSTRAPS

CHIP_RESET

GLCP_SYS_RSTPLL Bit Descriptions

Bit

Name

Description

63:44

RSVD

Reserved.

43:39

GLIUMULT

GLIU Multiplier (Bootstrap Dependent, see Table 6-87).

00000: Multiply by 1,....

11111: Multiply by 32.

38

GLIUDIV

GLIU Divide. When set, predivide the GLIU PLL input frequency by 2.

0: Do not predivide input. (Default)

1: Divide by 2.

37:33

COREMULT

CPU Core Multiplier (bootstrap dependent, see Table 6-87 on page 556).

00000: Multiply by 1,....

11111: Multiply by 32.

32

COREDIV

CPU Core Divide. When set, predivide the GLIU PLL input frequency by 2.

0: Do not predivide input. (Default)

1: Divide by 2.

31:26

SWFLAGS

Flags. Flags that are reset only by the POR# signal, not the CHIP_RESET (bit 0). They

are reset to 0 and can be used as flags in the boot code that survive CHIP_RESET.

25

GLIULOCK (RO)

Lock (Read Only). Lock signal from the system PLL. The worst-case lock time for a

AMD Geode™ LX processor PLL is 100 µs.

24

CORELOCK

(RO)

Lock (Read Only). Lock signal from the system PLL. The worst-case lock time for a

AMD Geode LX processor PLL is 100 µs.