3 chip fabrication information (glcp_fab), Glcp global power management controls, Glcp_glb_pm) – AMD Geode LX [email protected] User Manual

Page 547: Chip fabrication information (glcp_fab)

AMD Geode™ LX Processors Data Book

547

GeodeLink™ Control Processor Register Descriptions

33234H

6.14.2.3 Chip Fabrication Information (GLCP_FAB)

This read only register is used to track various fab, process, and product family parameters. It is meant for AMD internal use

only. Reads return reset value.

6.14.2.4 GLCP Global Power Management Controls (GLCP_GLB_PM)

MSR Address

4C00000Ah

Type

RO

Reset Value

00000000_00000001h

MSR Address

4C00000Bh

Type

R/W

Reset Value

00000000_00000000h

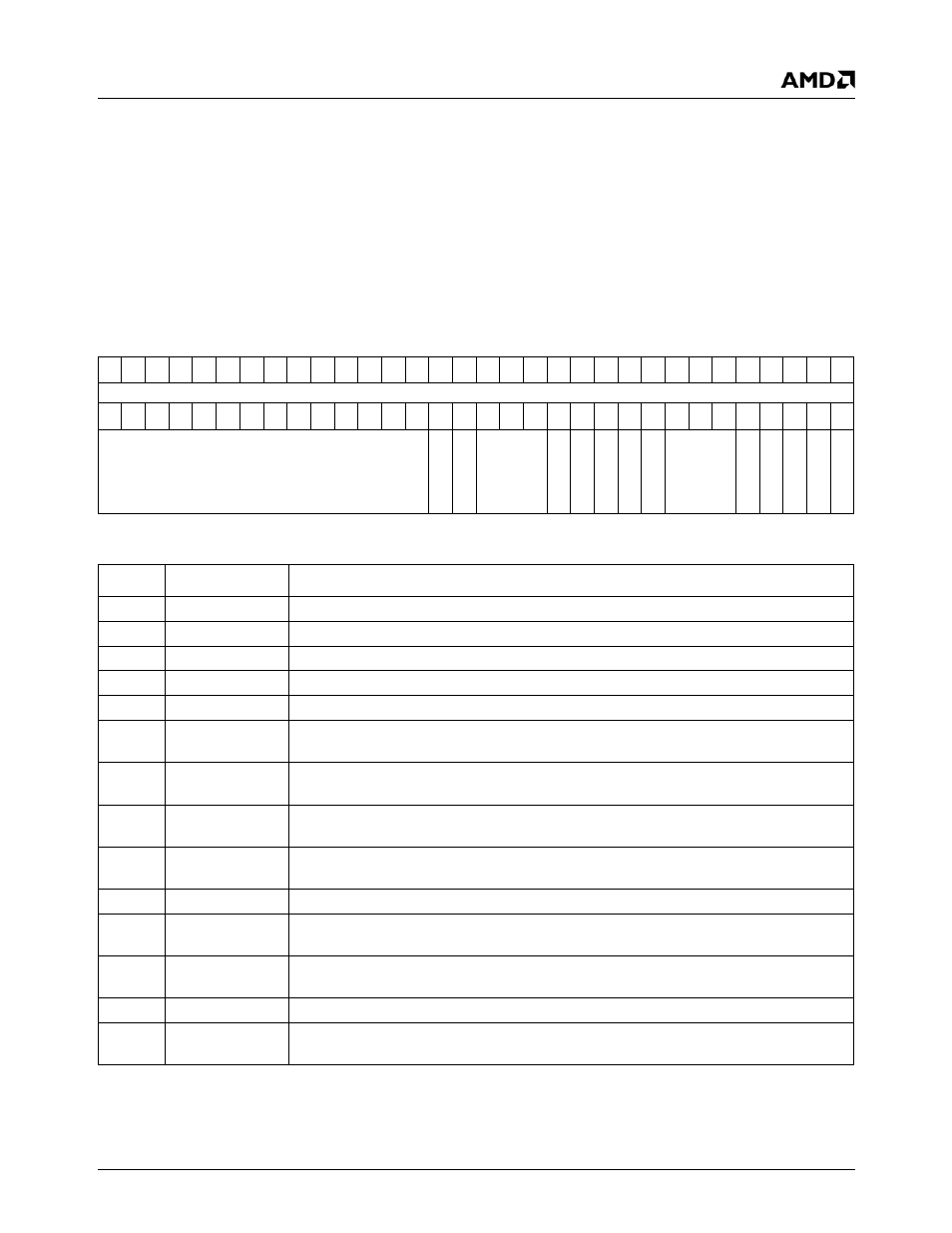

GLCP_GLB_PM Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

RSVD

DO

T

P

LL_EN

S

YSPLL_EN

RSVD

OUT_VP

OUT

_

G

IO

OUT

_

GLMC

OUT_PCI

OU

T_O

T

HE

R

RSVD

CLK_DL

Y_EN

CLK_DIS_EN

RSVD

RSVD

TH

T_EN

GLCP_GLB_PM Bit Descriptions

Bit

Name

Description

63:18

RSVD

Reserved.

17

DOTPLL_EN

DOTPLL Enable. Enables turning off the Dot clock PLL during sleep when high.

16

SYSPLL_EN

SYSPLL Enable. Enables turning off the system PLLs during sleep when high.

15:13

RSVD

Reserved.

12

OUT_VP

VP Outputs. When set, enables VP outputs to TRI_STATE during a sleep sequence.

11

OUT_GIO

GIO Outputs. When set, enables AMD Geode™ I/O companion (GIO) to TRI_STATE

device outputs during a sleep sequence.

10

OUT_GLMC

GLMC Outputs. When set, enables GLMC to TRI_STATE outputs during a sleep

sequence.

9

OUT_PCI

GLPCI Outputs. When set, enables GLPCI to TRI_STATE outputs during a sleep

sequence.

8

OUT_OTHER

Other Outputs. When set, enables TDBGO and SUSPA# to TRI_STATE during a sleep

sequence.

7:5

RSVD

Reserved.

4

CLK_DLY_EN

Clock Delay Enable. Enables gating off clock enables from a delay rather than

GLCP_CLK4ACK (MSR 4C000013h) when high.

3

CLK_DIS_EN

Clock Display Enable. Enables the assertion of internal signal, mb_clk_dis_req, during

a sleep sequence when high.

2:1

RSVD

Reserved.

0

THT_EN

Throttle Enable. Enables processor throttling functions. If this bit is low, all the functions

related to throttling are disabled (GLCP_TH_OD, GLCP_CNT, etc.).