Table 5-15, Region properties register map, Table 5-16 – AMD Geode LX [email protected] User Manual

Page 170: Read operations vs. region properties, Table 5-17, Write operations vs. region properties

170

AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

Region Properties

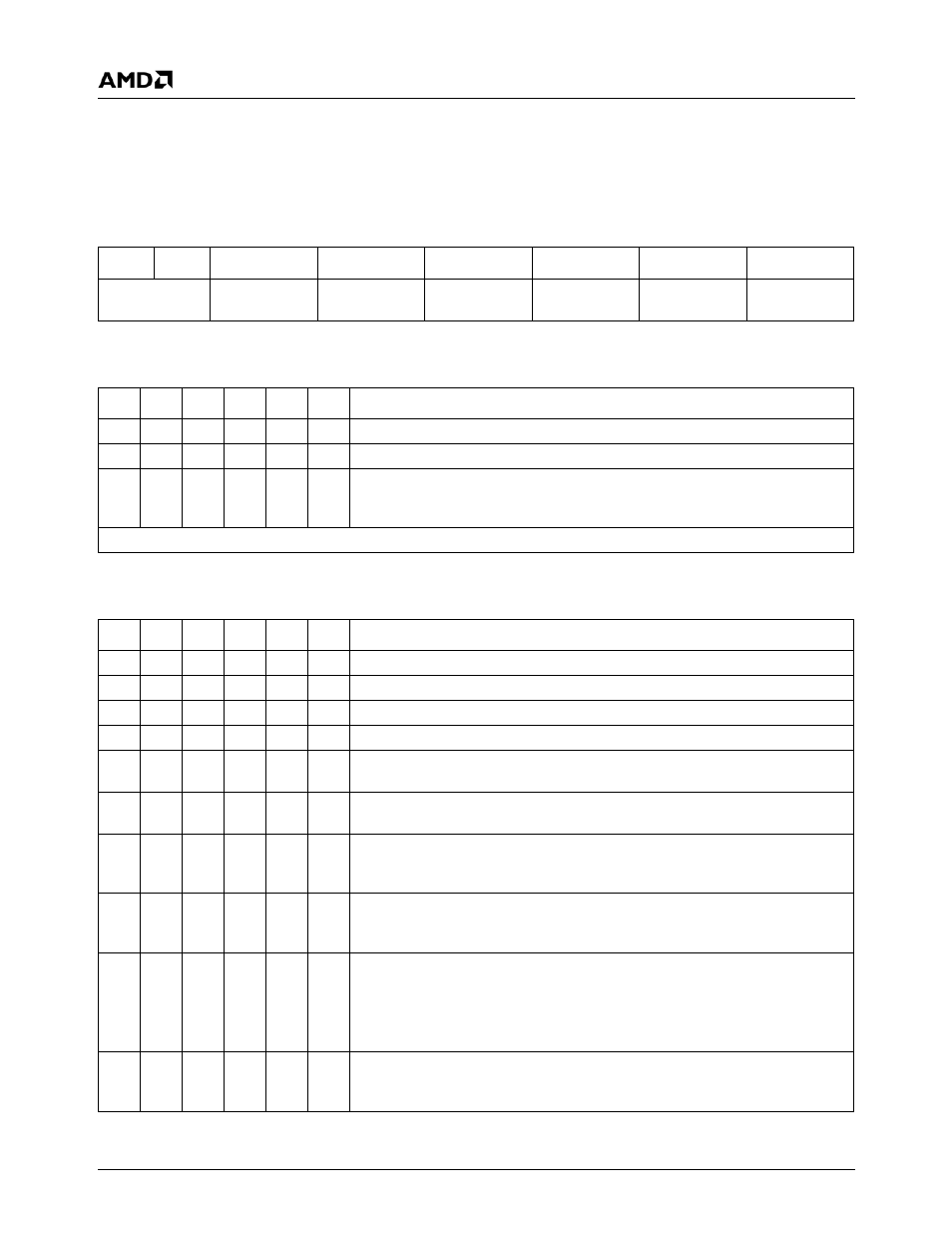

The region properties consist of an 8-bit field as shown in Table 5-15. Table 5-16 and Table 5-17 describe the various region

properties effects on read and write operations. Note that the cache is always interrogated even in regions that are not

cacheable, and read hits are serviced from the cache while write hits update the cache and are sent to the bus using the

region’s write semantics.

Table 5-15. Region Properties Register Map

7

6

5

4

3

2

1

0

(RSVD)

Reserved

WS

(Write-serialize)

WC

(Write-combine)

WT

(Write-through)

WP

(Write-protect)

WA

(Write-allocate)

CD

(Cache Disable)

Table 5-16. Read Operations vs. Region Properties

WS

WC

WT

WP

WA

CD

Description

0

x

x

x

x

0

Cacheable. Read misses cause a cache line to be allocated.

1

x

x

x

x

0

Undefined State. Unpredictable behavior occurs.

x

x

x

x

x

1

Uncacheable. Reads are sent unmodified to the bus. Cache is still interro-

gated and provides data for read hits. Used for accessing memory-mapped

devices.

Note:

“x” indicates setting or clearing this bit has no effect.

Table 5-17. Write Operations vs. Region Properties

WS

WC

WT

WP

WA

CD

Description

x

x

x

1

x

x

Write-protected. Writes to the region are discarded.

1

x

x

x

x

0

Undefined State. Unpredictable behavior occurs.

x

1

x

x

x

0

Undefined State. Unpredictable behavior occurs.

x

x

x

x

1

1

Undefined State. Unpredictable behavior occurs.

0

0

0

0

0

0

Write-back Cacheable. Write misses are sent to the bus, a cache line is not

allocated on a write miss.

0

0

0

0

1

0

Write-back Cacheable/Write-allocate. Write misses allocate a line in the

cache.

0

0

1

0

x

0

Write-through cacheable. Write misses do not allocate a line in the cache.

Write hits update the cache but do not mark the line as dirty. All writes are sent

to the bus.

0

0

0

0

0

1

Uncacheable. All writes are sent to the bus in strict program order without any

combining. Write hits still update the cache. Traditionally used for accessing

memory-mapped devices (but see write-burstable below).

1

0

0

0

0

1

Uncacheable. All writes are sent to the bus in strict program order without any

combining. Write hits still update the cache. Traditionally used for accessing

memory-mapped devices (but see write-burstable below).

Write-serialize. Limit the number of outstanding writes to the value of the

WSREQ field in DM_CONFIG0_MSR (MSR 00001800h[46:44]).

0

1

0

0

0

1

Write-combined (uncacheable). Writes to the same cache line may be com-

bined. Multiple writes to the same byte results in a single write with the last

value specified. Write order is not preserved; ideal for use with frame buffers.