AMD Geode LX [email protected] User Manual

Page 302

302

AMD Geode™ LX Processors Data Book

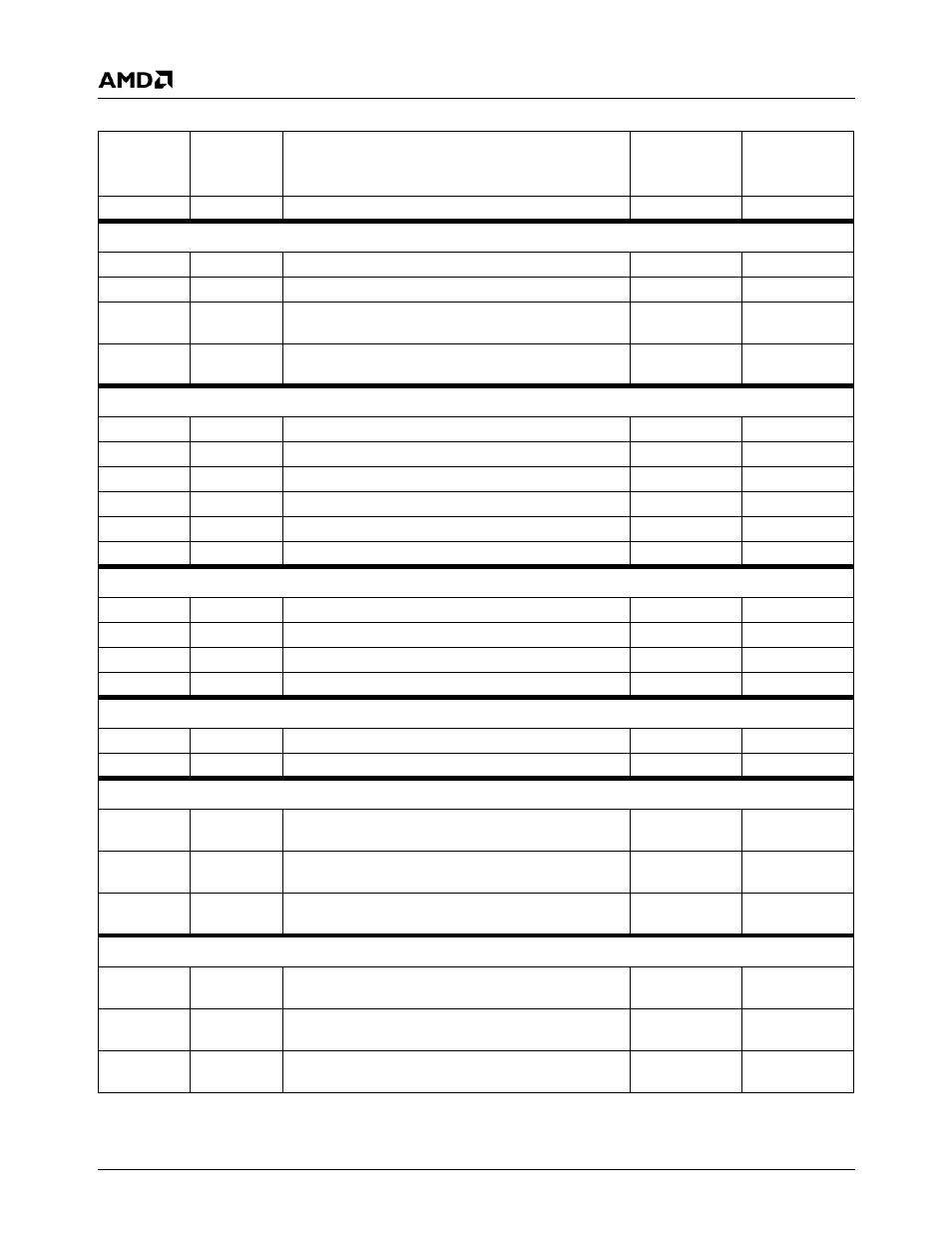

Display Controller Register Descriptions

33234H

R/W

DC Dirty/Valid RAM Access (DC_DV_ACCESS)

Graphics Scaling Control Registers

DC Graphics Filter Scale (DC_GFX_SCALE)

DC IRQ/Filter Control (DC_IRQ_FILT_CTL)

098h

R/W

DC Filter Coefficient Data Register 1

(DC_FILT_COEFF1)

xxxxxxxxh

DC Filter Coefficient Data Register 2

(DC_FILT_COEFF2)

VBI Control Registers

DC VBI Even Control (DC_VBI_EVEN_CTL)

DC VBI Odd Control (DC_VBI_ODD_CTL)

DC VBI Horizontal Control (DC_VBI_HOR)

DC VBI Odd Line Enable (DC_VBI_LN_ODD)

DC VBI Even Line Enable (DC_VBI_LN_EVEN)

DC VBI Pitch and Size (DC_VBI_PITCH)

Color Key Control Registers

DC Color Key Mask (DC_CLR_KEY_MASK)

DC Color Key Horizontal Position (DC_CLR_KEY_X)

DC Color Key Vertical Position (DC_CLR_KEY_Y)

Interrupt and GenLock Registers

DC GenLock Control (DC_GENLK_CTL)

Even Field Video Address Registers

DC Even Field Video Y Start Address Offset

(DC_VID_EVEN_Y_ST_OFFSET)

DC Even Field Video U Start Address Offset

(DC_VID_EVEN_U_ST_OFFSET)

DC Even Field Video V Start Address Offset

(DC_VID_EVEN_V_ST_OFFSET)

Even Field Vertical Timing Registers

DC Vertical and Total Timing for Even Fields

(DC_V_ACTIVE_EVEN_TIMING)

DC CRT Vertical Blank Timing for Even Fields

(DC_V_BLANK_EVEN_TIMING)

DC CRT Vertical Sync Timing for Even Fields

(DC_V_SYNC_EVEN_TIMING)

Table 6-47. DC Configuration Control Register Summary (Continued)

DC

Memory

Offset

Type

Register Name

Reset Value

Reference