7 palette access fifo diagnostic registers, 1 dc palette address (dc_pal_address), Dc palette address (dc_pal_address) – AMD Geode LX [email protected] User Manual

Page 335

AMD Geode™ LX Processors Data Book

335

Display Controller Register Descriptions

33234H

6.6.7

Palette Access FIFO Diagnostic Registers

The Palette Access registers are used for accessing the internal palette RAM and extensions. In addition to the standard

256 entries for color translation, the palette has extensions for cursor colors and overscan (border) color.

The diagnostics registers enable testability of the display FIFO and compression FIFO.

6.6.7.1

DC Palette Address (DC_PAL_ADDRESS)

This register should be written with the address (index) location to be used for the next access to the (DC_PAL_DATA regis-

ter DC Memory Offset 074h).

DC Memory Offset 070h

Type

R/W

Reset Value

xxxxxxxxh

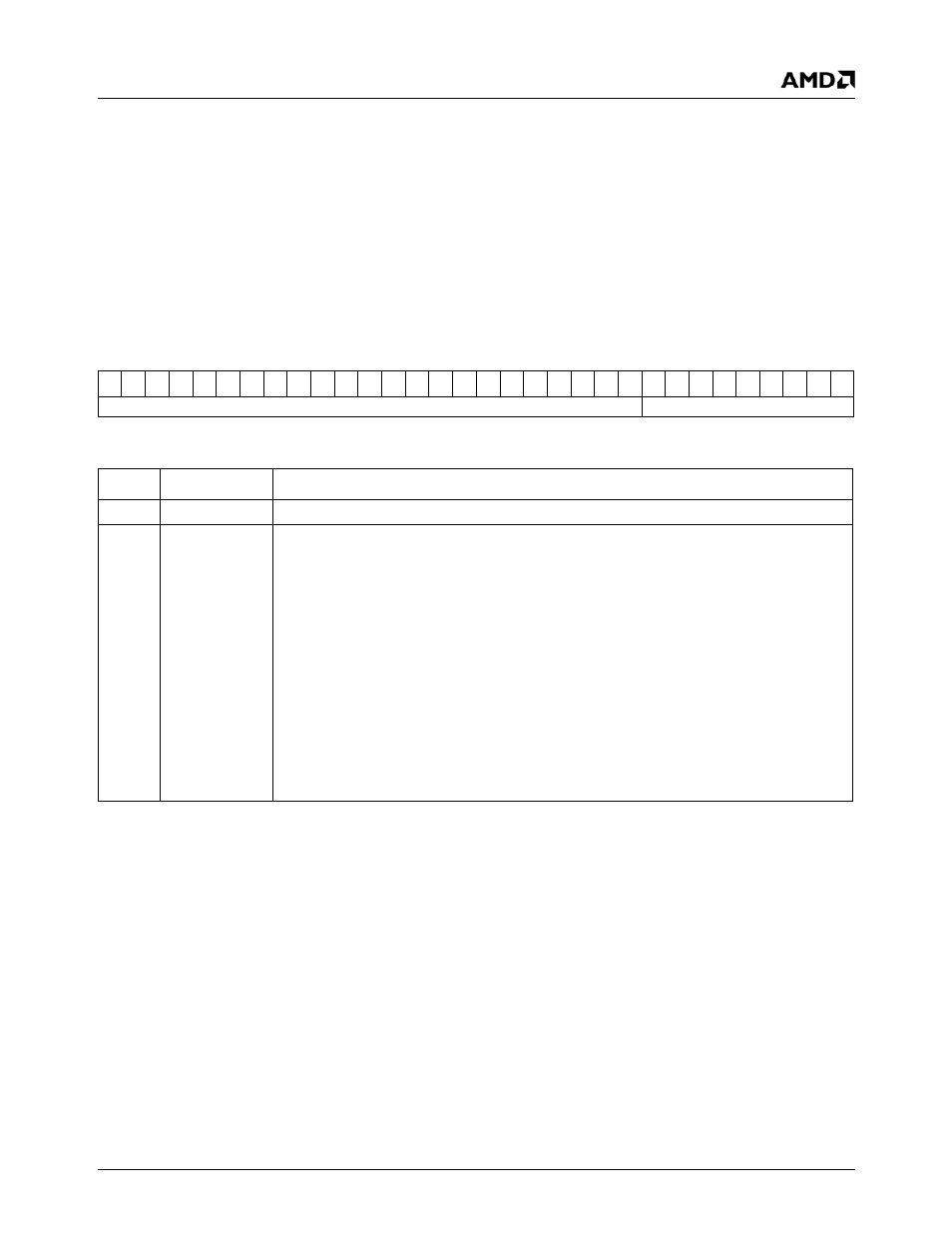

DC_PAL_ADDRESS Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

RSVD

PAL_ADDR

DC_PAL_ADDRESS Bit Descriptions

Bit

Name

Description

31:9

RSVD

Reserved.

8:0

PAL_ADDR

PAL Address. This 9-bit field specifies the address to be used for the next access to the

DC_PAL_DATA register (DC Memory Offset 074h). Each access to the data register auto-

matically increments the palette address register. If non-sequential access is made to the

palette, the address register must be loaded between each non-sequential data block. The

address ranges are as follows:

Address

Color

0h - FFh

Standard Palette Colors

100h

Cursor Color 0

101h

Cursor Color 1

102h

RSVD

103h

RSVD

104h

Overscan Color

105h - 1FFh

Not Valid

Note that in general, 24-bit values are loaded for all color extensions. However, if a 16-bpp

mode is active, only the appropriate most significant bits are used (5:5:5 or 5:6:5).