AMD Geode LX [email protected] User Manual

Page 105

AMD Geode™ LX Processors Data Book

105

CPU Core Register Descriptions

33234H

Bus Controller Configuration 1 MSR

(BC_CONFIG1_MSR)

00001904h

RO

Reserved Status MSR (RSVD_STS_MSR)

00000000_00000000h

Real Time Stamp Counter MSR (RTSC_MSR)

TSC and RTSC Low DWORDs MSR

(RTSC_TSC_MSR)

L2 Cache Configuration MSR (L2_CONFIG_MSR)

L2 Cache Status MSR (L2_STATUS_MSR)

L2 Cache Index MSR (L2_INDEX_MSR)

L2 Cache Data MSR (L2_DATA_MSR)

L2 Cache Tag with Increment MSR

(L2_TAG_I_MSR)

L2 Cache Built-In Self-Test MSR (L2_BIST_MSR)

L2 Cache Treatment Control MSR

(L2_TRTMNT_CTL_MSR)

Bus Controller Extended Debug Registers 1 and 0

MSR (BXDR1_BXDR0_MSR)

Bus Controller Extended Debug Registers 3 and 2

MSR (BXDR3_BXDR2_MSR)

Bus Controller Extended Debug Registers 6 and 7

MSR (BXDR6_BXDR7_MSR)

Bus Controller Debug Register 0 MSR

(BDR0_MSR)

Bus Controller Debug Register 1 MSR

(BDR1_MSR)

Bus Controller Debug Register 2 MSR

(BDR2_MSR)

Bus Controller Debug Register 3 MSR

(BDR3_MSR)

Bus Controller Debug Register 6 MSR

(BDR6_MSR)

Bus Controller Debug Register 7 MSR

(BDR7_MSR)

Memory Subsystem Array Control Enable MSR

(MSS_ARRAY_CTL_EN_MSR)

Memory Subsystem Array Control 0 MSR

(MSS_ARRAY_CTL0_MSR)

Memory Subsystem Array Control 1 MSR

(MSS_ARRAY_CTL1_MSR)

Memory Subsystem Array Control 2 MSR

(MSS_ARRAY_CTL2_MSR)

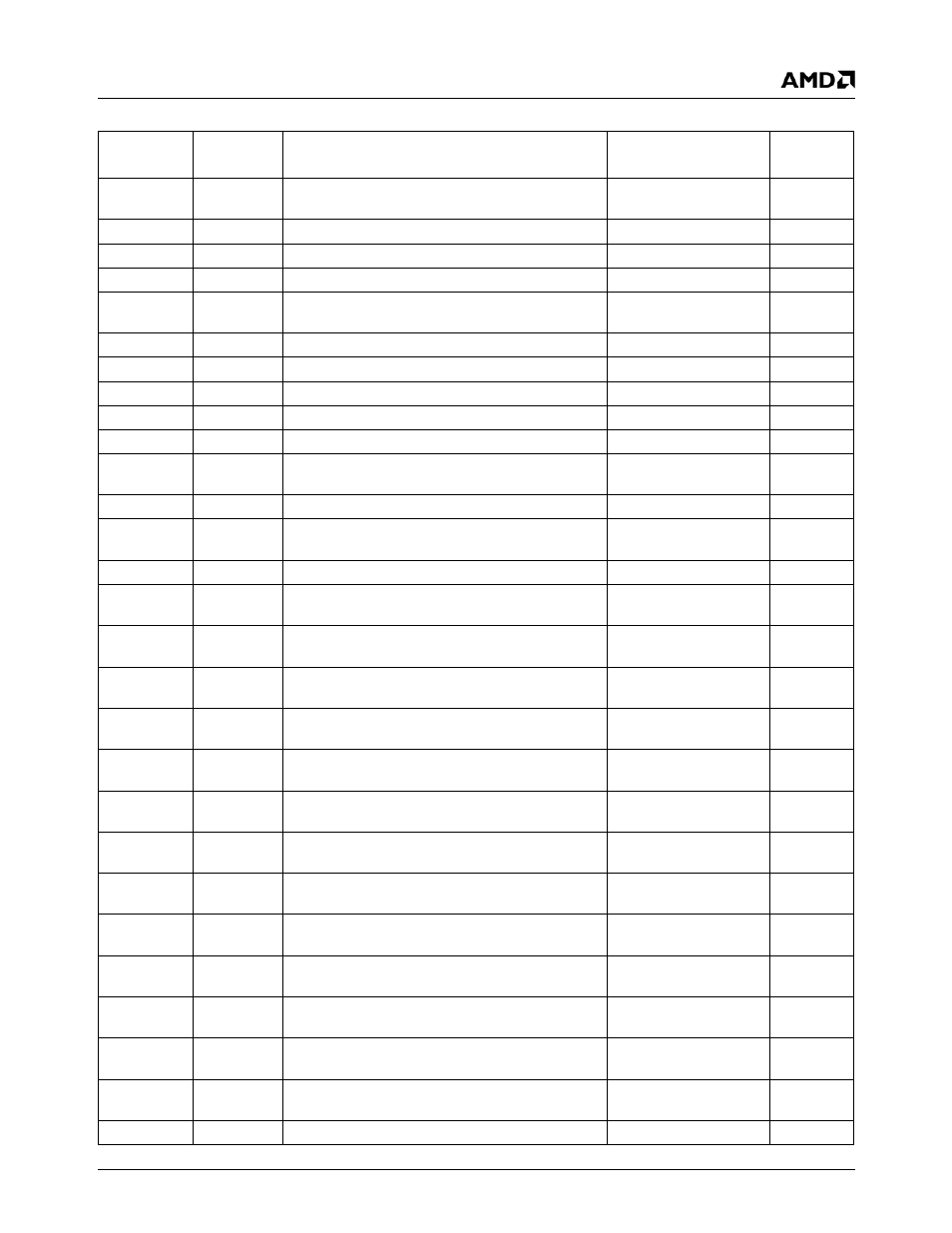

Table 5-13. CPU Core Specific MSRs Summary (Continued)

MSR

Address

Type

Register Name

Reset Value

Reference