AMD Geode LX [email protected] User Manual

Page 640

640

AMD Geode™ LX Processors Data Book

Instruction Set

33234H

OUT Output to Port

-

-

-

-

-

-

-

-

-

m

Fixed Port

E [011w] #

8

8/23

Variable Port

E [111w]

8

8/23

OUTS Output String

6 [111w]

12

12/26

-

-

-

-

-

-

-

-

-

b

h,m

PAUSE

7

POP Pop Value off Stack

-

-

-

-

-

-

-

-

-

b

h,i,j

Register

8F [mod 000 r/m]

1

1

Memory

8F [mod 000 r/m]

3

3

Register (short form)

5 [1 reg]

1

1

DS

1F

1

6/13

ES

07

1

6/13

SS

17

1

7/13

FS

0F A1

1

6/13

GS

0F 9A

1

6/13

POPA Pop All General Registers

61

8

8

-

-

-

-

-

-

-

-

-

b

h

POPF Pop Stack into FLAGS

9D

2

2

x

x

x

x

x

x

x

x

x

b

h,n

PREFIX BYTES

-

-

-

-

-

-

-

-

-

m

Assert Hardware LOCK Prefix

F0

Address Size Prefix

67

Operand Size Prefix

66

Segment Override Prefix

-CS

-DS

-ES

-FS

-GS

-SS

2E

3E

26

64

65

36

PUSH Push Value onto Stack

-

-

-

-

-

-

-

-

-

b

h

Register/Memory

FF [mod 110 r/m]

1/2

1/2

Register (short form)

5 [0 reg]

1

1

CS

0E

1

1

SS

16

1

1

DS

1E

1

1

ES

06

1

1

FS

0F A0

1

1

GS

0F A8

1

1

Immediate

6 [10s0] ###

1

1

PUSHA Push All General Registers

60

8

8

-

-

-

-

-

-

-

-

-

b

h

PUSHF Push FLAGS Register

9C

2

2

-

-

-

-

-

-

-

-

-

b

h

RCL Rotate Through Carry Left

Register/Memory by 1

D [000w] [mod 010 r/m]

2

2

x

-

-

-

-

-

-

-

x

b

h

Register/Memory by CL

D [001w] [mod 010 r/m]

4-6

4-6

u

-

-

-

-

-

-

-

x

Register/Memory by Immediate

C [000w] [mod 010 r/m] #

4-6

4-6

u

-

-

-

-

-

-

-

x

RCR Rotate Through Carry Right

Register/Memory by 1

Register/Memory by CL

Register/Memory by Immediate

b

h

D [000w] [mod 011 r/m]

3-5

3-4

x

-

-

-

-

-

-

-

x

D [001w] [mod 011 r/m]

4-7

4-7

u

-

-

-

-

-

-

-

x

C [000w] [mod 011 r/m] #

4-7

4-7

u

-

-

-

-

-

-

-

x

RDM Leave Debug Management Mode

0F 3A

36+

36+

x

x

x

x

x

x

x

x

x

s, u

s, u

RDMSR Read Tmodel Specific Register (Note 1)

0F 32

5

5

-

-

-

-

-

-

-

-

-

RDPMC (Note 1)

7

7

RDTSC Read Time Stamp Counter (Note 1)

0F 31

5

5

-

-

-

-

-

-

-

-

-

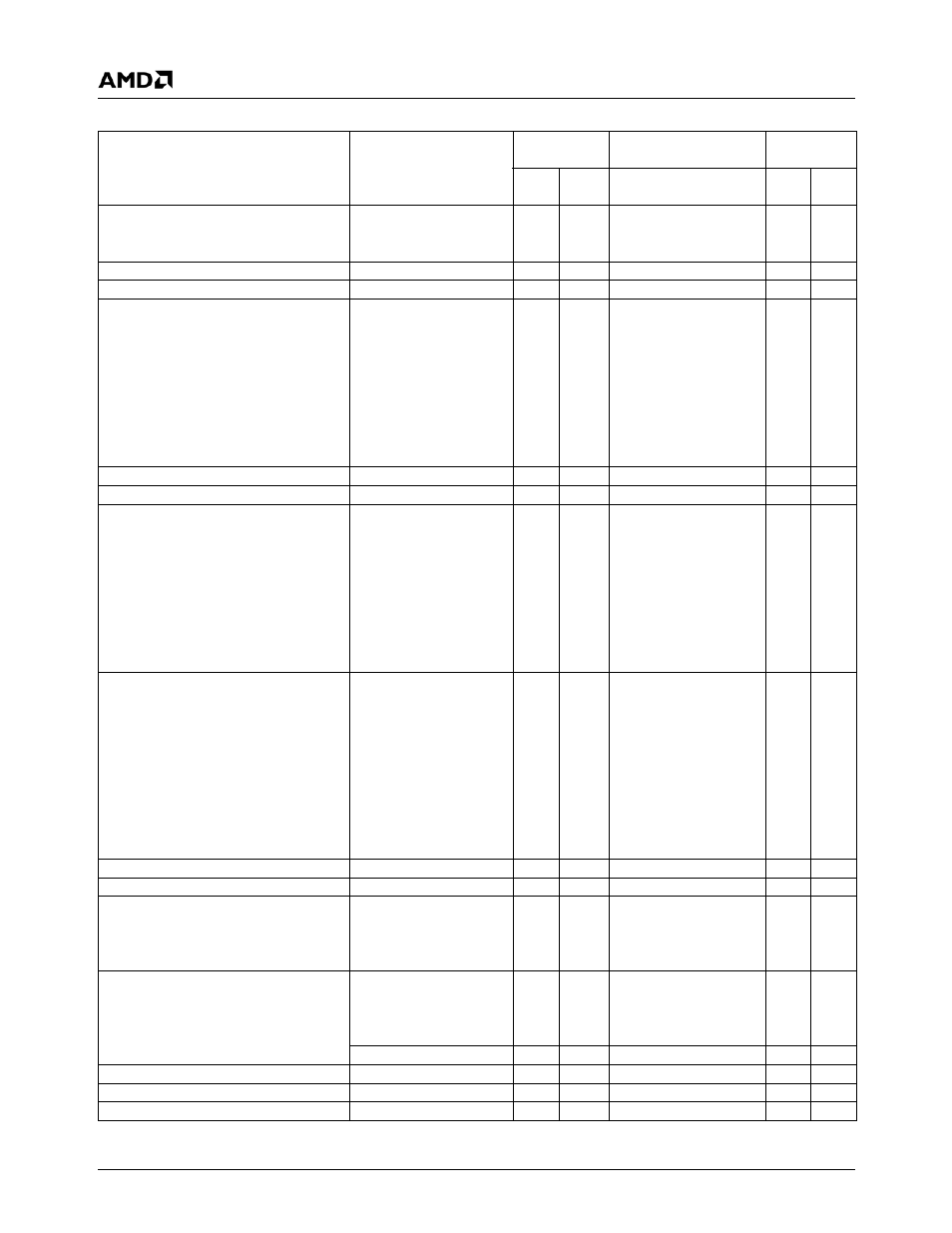

Table 8-26. Processor Core Instruction Set (Continued)

Instruction

Opcode

Clock Count

(Reg/Cache Hit)

Flags

Notes

Real

Mode

Prot’d

Mode

O D I

T

S Z

A P C

F

F

F

F

F

F

F

F

F

Real

Mode

Prot’d

Mode