AMD Geode LX [email protected] User Manual

Page 64

64

AMD Geode™ LX Processors Data Book

GLIU Register Descriptions

33234H

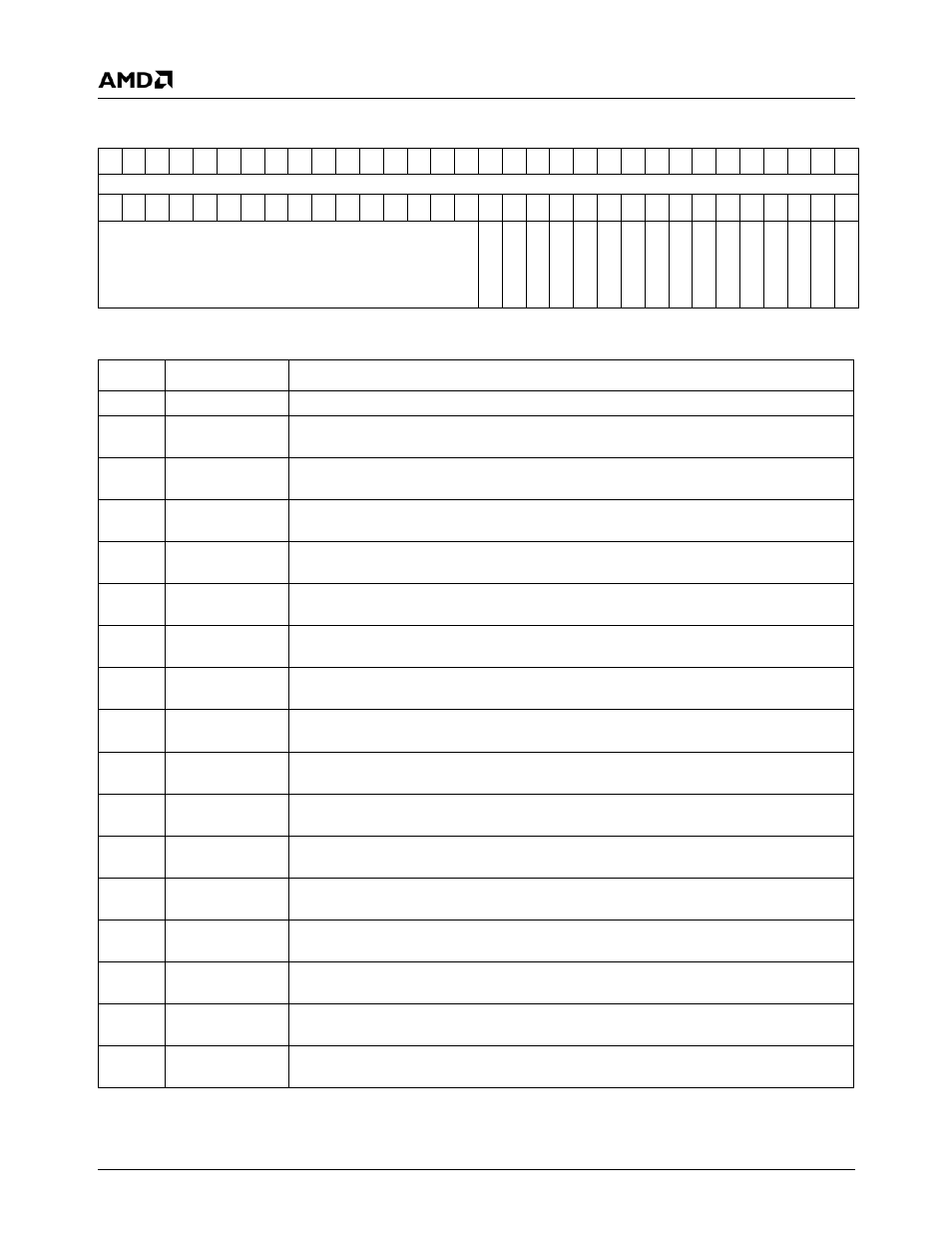

AERR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

RSVD

AERR_MASK7

AERR_MASK6

AERR_MASK5

AERR_MASK4

AERR_MASK3

AERR_MASK2

AERR_MASK1

AERR_MASK0

AE

R

R

7

AE

R

R

6

AE

R

R

5

AE

R

R

4

AE

R

R

3

AE

R

R

2

AE

R

R

1

AE

R

R

0

AERR Bit Descriptions

Bit

Name

Description

63:16

RSVD

Reserved.

15

AERR_MASK7

Asynchronous Error Mask for Port 7. (GLIU0 = Not Used; GLIU1 = Not Used.) Write 0

to allow Port 7 to generate an AERR. AERR status is reported in bit 7.

14

AERR_MASK6

Asynchronous Error Mask for Port 6. (GLIU0 = Not Used; GLIU1 = SB.) Write 0 to

allow Port 6 to generate an AERR. AERR status is reported in bit 6.

13

AERR_MASK5

Asynchronous Error Mask for Port 5. (GLIU0 = GP; GLIU1 = VIP.) Write 0 to allow Port

5 to generate an AERR. AERR status is reported in bit 5.

12

AERR_MASK4

Asynchronous Error Mask for Port 4. (GLIU0 = DC; GLIU1 = GLPCI.) Write 0 to allow

Port 4 to generate an AERR. AERR status is reported in bit 4.

11

AERR_MASK3

Asynchronous Error Mask for Port 3. (GLIU0 = CPU Core; GLIU1 = GLCP.) Write 0 to

allow Port 3 to generate an AERR. AERR status is reported in bit 3.

10

AERR_MASK2

Asynchronous Error Mask for Port 2. (GLIU0 = Interface to GLIU1; GLIU1 = VP.) Write

0 to allow Port 2 to generate an AERR. AERR status is reported in bit 2.

9

AERR_MASK1

Asynchronous Error Mask for Port 1. (GLIU0 = GLMC; GLIU1 = Interface to GLIU0.)

Write 0 to allow Port 1 to generate an AERR. AERR status is reported in bit 1.

8

AERR_MASK0

Asynchronous Error Mask for Port 0. (GLIU0 = GLIU; GLIU1 = GLIU.) Write 0 to allow

Port 0 to generate an AERR. AERR status is reported in bit 0.

7

AERR_FLAG7

(RO)

Asynchronous Error for Port 7 (Read Only). (GLIU0 = Not Used; GLIU1 = Not Used.) If

1, indicates that an AERR was generated by Port 7. Cleared by source.

6

AERR_FLAG6

(RO)

Asynchronous Error for Port 6 (Read Only). (GLIU0 = Not Used; GLIU1 = SB.) If 1,

indicates that an AERR was generated by Port 6. Cleared by source.

5

AERR_FLAG5

(RO)

Asynchronous Error for Port 5 (Read Only). (GLIU0 = GP; GLIU1 = VIP.) If 1, indicates

that an AERR was generated by Port 5. Cleared by source.

4

AERR_FLAG4

(RO)

Asynchronous Error for Port 4 (Read Only). (GLIU0 = DC; GLIU1 = GLPCI.) If 1, indi-

cates that an AERR was generated by Port 4. Cleared by source.

3

AERR_FLAG3

(RO)

Asynchronous Error for Port 3 (Read Only). (GLIU0 = CPU Core; GLIU1 = GLCP.) If 1,

indicates that an AERR was generated by Port 3. Cleared by source.

2

AERR_FLAG2

(RO)

Asynchronous Error for Port 2 (Read Only). (GLIU0 = Interface to GLIU1; GLIU1 =

VP.) If 1, indicates that an AERR was generated by Port 2. Cleared by source.

1

AERR_FLAG1

(RO)

Asynchronous Error for Port 1 (Read Only). (GLIU0 = GLMC; GLIU1 = Interface to

GLIU0.) If 1, indicates that an AERR was generated by Port 1. Cleared by source.

0

AERR_FLAG0

(RO)

Asynchronous Error for Port 0 (Read Only). (GLIU0 = GLIU; GLIU1 = GLIU.) If 1, indi-

cates that an AERR was generated by Port 0. Cleared by source.