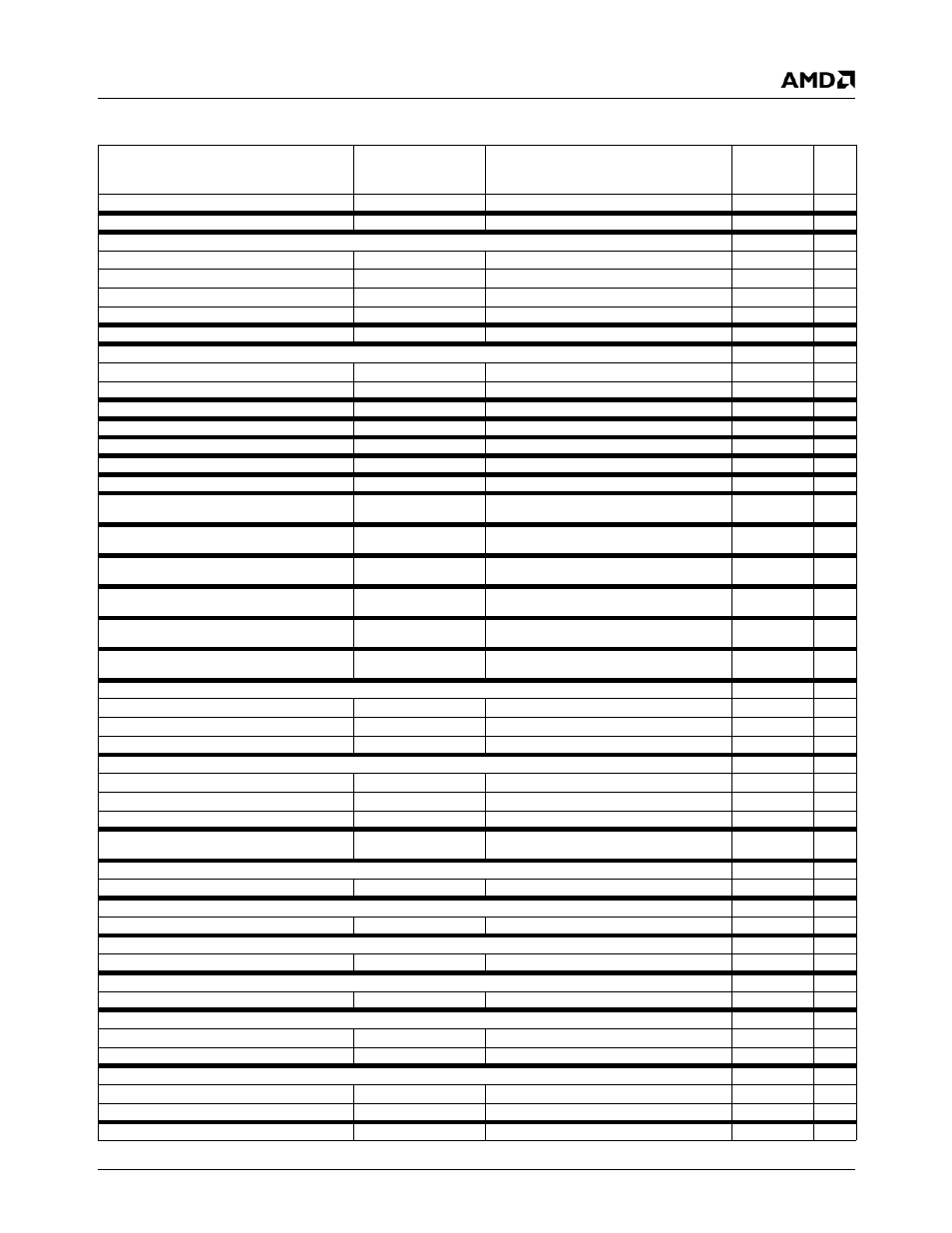

Table 8-29, Fpu instruction set, Table 8-29. fpu instruction set – AMD Geode LX [email protected] User Manual

Page 667

AMD Geode™ LX Processors Data Book

667

Instruction Set

33234H

Table 8-29. FPU Instruction Set

FPU Instruction

Opcode

Operation

Clock Ct

Single/Dbl

(or extended)

Notes

F2XM1 Function Evaluation 2x-1

D9 F0

TOS <--- 2

TOS

-1

145 - 166

2

FABS Floating Absolute Value

D9 E1

TOS <--- | TOS |

1

3

FADD Floating Point Add

Top of Stack

DC [1100 0 n]

ST(n) <--- ST(n) + TOS

1/6

80-bit Register

D8 [1100 0 n]

TOS <--- TOS + ST(n)

1/6

64-bit Real

DC [mod 000 r/m]

TOS <--- TOS + M.DR

1/6

32-bit Real

D8 [mod 000 r/m]

TOS <--- TOS + M.SR

1/6

FADDP Floating Point Add, Pop

DE [1100 0 n]

ST(n) <--- ST(n) + TOS; then pop TOS

1/6

FIADD Floating Point Integer Add

32-bit integer

DA [mod 000 r/m]

TOS <--- TOS + M.SI

2/7

16-bit integer

DE [mod 000 r/m]

TOS <--- TOS + M.WI

2/7

FCHS Floating Change Sign

D9 E0

TOS <--- - TOS

1

FCLEX Clear Exceptions

(9B) DB E2

Wait then Clear Exceptions

1+

2

FNCLEX Clear Exceptions

DB E2

Clear Exceptions

1+

2

FCMOVB Floating Point Conditional Move if Below

DA [1100 0 n]

If (CF=1) ST(0) <--- ST(n)

1

3

FCMOVE Floating Point Conditional Move if Equal

DA [1100 1 n]

If (ZF=1) ST(0) <--- ST(n)

1

3

FCMOVBE Floating Point Conditional Move if

Below or Equal

DA [1101 0 n]

If (CF=1 or ZF=1) ST(0) <--- ST(n)

1

3

FCMOVU Floating Point Conditional Move if

Unordered

DA [1101 1 n]

If (PF=1) ST(0) <--- ST(n)

1

3

FCMOVNB Floating Point Conditional Move if

Not Below

DB [1100 0 n]

If (CF=0) ST(0) <--- ST(n)

1

3

FCMOVNE Floating Point Conditional Move if

Not Equal

DB [1100 1 n]

If (ZF=0) ST(0) <--- ST(n)

1

3

FCMOVNBE Floating Point Conditional Move if

Not Below or Equal

DB [1101 0 n]

If (CF=0 and ZF=0) ST(0) <--- ST(n)

1

3

FCMOVNU Floating Point Conditional Move if

Not Unordered

DB [1101 1 n]

If (PF=0) ST(0) <--- ST(n)

1

3

FCOM Floating Point Compare

80-bit Register

D8 [1101 0 n]

CC set by TOS - ST(n)

1/6

64-bit Real

DC [mod 010 r/m]

CC set by TOS - M.DR

1/6

32-bit Real

D8 [mod 010 r/m]

CC set by TOS - M.SR

1/6

FCOMP Floating Point Compare, Pop

80-bit Register

D8 [1101 1 n]

CC set by TOS - ST(n); then pop TOS

1/6

64-bit Real

DC [mod 011 r/m]

CC set by TOS - M.DR; then pop TOS

1/6

32-bit Real

D8 [mod 011 r/m]

CC set by TOS - M.SR; then pop TOS

1/6

FCOMPP Floating Point Compare, Pop

Two Stack Elements

DE D9

CC set by TOS - ST(1); then pop TOS and ST(1)

1/6

FCOMI Floating Point Compare Real and Set EFLAGS

80-bit Register

DB [1111 0 n]

EFLAG set by TOS - ST(n)

1/6

FCOMIP Floating Point Compare Real and Set EFLAGS, Pop

80-bit Register

DF [1111 0 n]

EFLAG set by TOS - ST(n); then pop TOS

1/6

FUCOMI Floating Point Unordered Compare Real and Set EFLAGS

80-bit Integer

DB [1110 1 n]

EFLAG set by TOS - ST(n)

1/6

FUCOMIP Floating Point Unordered Compare Real and Set EFLAGS, Pop

80-bit Integer

DF [1110 1 n]

EFLAG set by TOS - ST(n); then pop TOS

1/6

FICOM Floating Point Integer Compare

32-bit integer

DA [mod 010 r/m]

CC set by TOS - M.WI

2/7

16-bit integer

DE [mod 010 r/m]

CC set by TOS - M.SI

2/7

FICOMP Floating Point Integer Compare, Pop

32-bit integer

DA [mod 011 r/m]

CC set by TOS - M.WI; then pop TOS

2/7

16-bit integer

DE [mod 011 r/m

CC set by TOS - M.SI; then pop TOS

2/7

FCOS Function Evaluation: Cos(x)

D9 FF

TOS <--- COS(TOS)

146 - 215

1