14 glcp dot clock pll control (glcp_dotpll), Table 6-88, Glcp dot clock pll control (glcp_dotpll) – AMD Geode LX [email protected] User Manual

Page 557: 000000d7_02000000h

AMD Geode™ LX Processors Data Book

557

GeodeLink™ Control Processor Register Descriptions

33234H

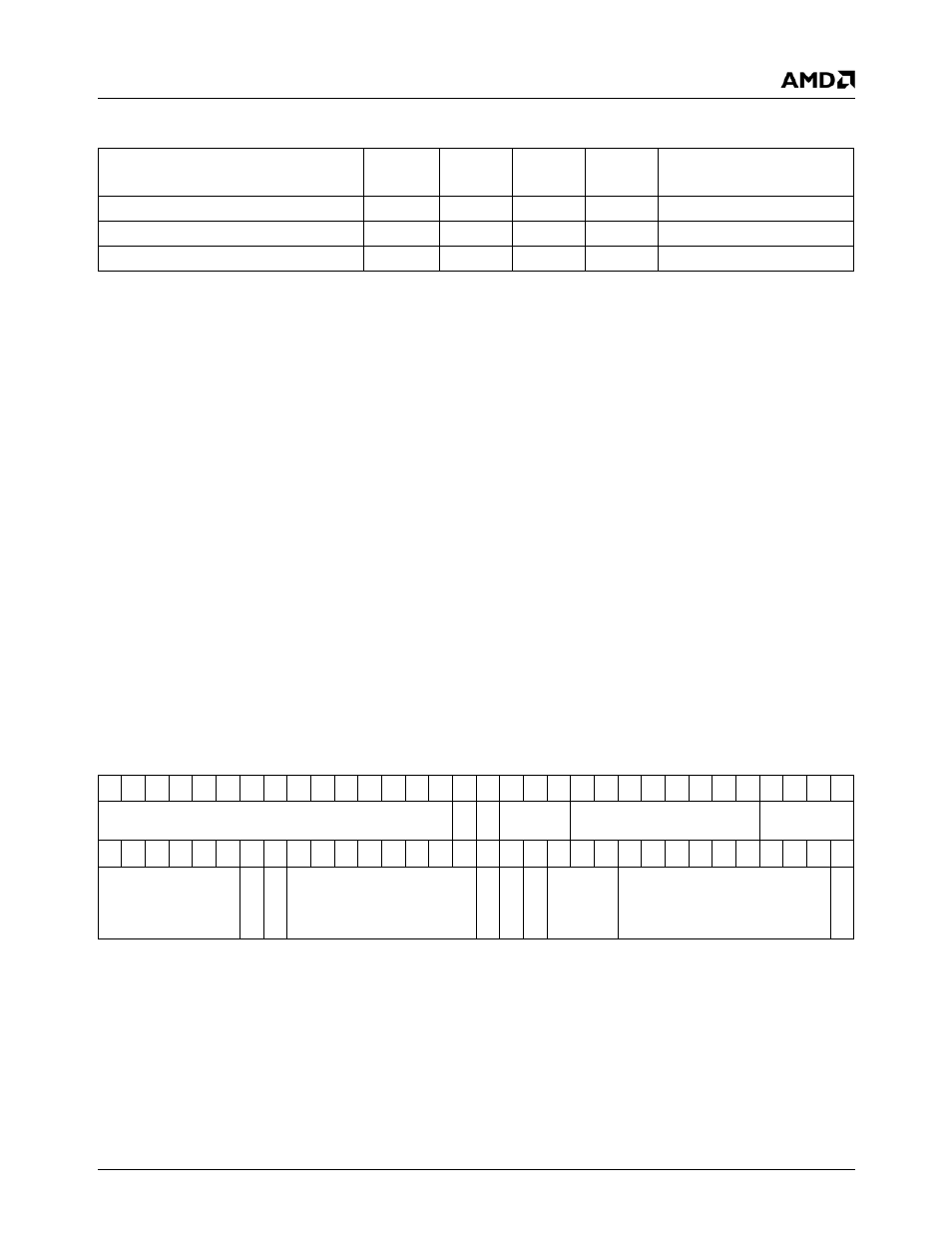

6.14.2.14 GLCP Dot Clock PLL Control (GLCP_DOTPLL)

This register does not include hardware handshake controls like the GLCP_SYS_RSTPLL register (MSR 4C000014h), so

care should be taken when changing the settings. For example, to change the DIV settings: write the register with the DOT-

RESET bit (bit 0) set and either in the same write or another write change the DIV settings; read the register until the LOCK

bit (bit 25) goes active (or until a timeout occurs, if desired); write the register with the same DIV settings and with the DOT-

RESET bit clear. The MDIV, NDIV, and PDIV (bits [46:32]) settings work in conjunction to create the internal DOTCLK using

this equation:

For example, with bits [46:32] in the GLCP_DOTPLL register set to 0x00D7 (reset), the Dot clock frequency that the DC and

VP would run with would be:

However, not all MDIV, NDIV, and PDIV settings lock and not all that lock have good long-term jitter characteristics. The PLL

resets to 25.0565 MHz for VGA monitors assuming a 14.31818 MHz input. A 27 MHz input will successfully lock at about 47

MHz, and should then be changed to the desired pixel rate.

Table 6-88. Bootstrap Bit Settings and Reset State of GLCP_SYS_RSTPLL (PW1 and IRQ13 vary)

{PW1,IRQ13,PW0,SUSPA#,GNT#[2:0]}

same as GLCP_SYS_RSTPLL[7:1]

CPU

Speed

CORE

MULT

GLIU

Speed

GLIU

MULT

GLCP_SYS_RSTPLL

Reset Value

0100000

Bypass

11

Bypass

7

00000396_00001840h

1000001

166

4

166

4

00000249_03000082h

1110111

500

14

400

11

000005DD_030000EEh

MSR Address

4C000015h

Type

R/W

Reset Value

000000D7_02000000h

Fout

Fin

NDIV

1

+

(

)

MDIV

1

+

(

) PDIV 1

+

(

)

⋅

---------------------------------------------------------------

⋅

=

Fout

14.318MHz

13

1

+

(

)

0

1

+

(

) 7 1

+

(

)

----------------------------------

⋅

25.0565MHz

=

=

GLCP_DOTPLL Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

DIV4

RSVD

MDIV

NDIV

PDIV

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

SWFLAGS

LOCK

HA

L

F

P

IX

RSVD

B

Y

P

ASS

PD

CAPEN

RSVD

RSVD

DO

TRESET