AMD Geode LX [email protected] User Manual

Page 101

AMD Geode™ LX Processors Data Book

101

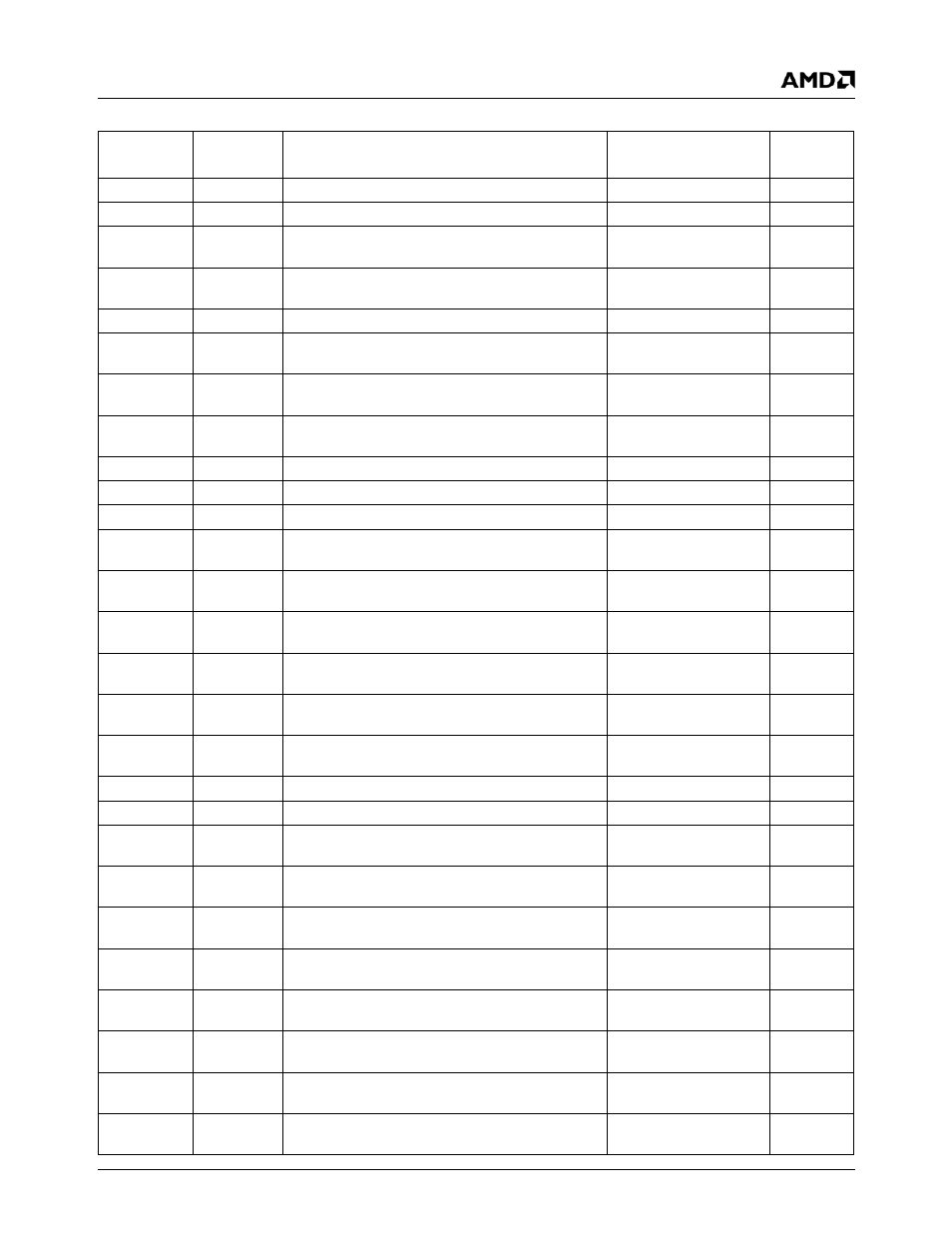

CPU Core Register Descriptions

33234H

GS Segment Base/Limit MSR (GS_BASE_MSR)

LDT Segment Base/Limit MSR (LDT_BASE_MSR)

Temp Segment Base/Limit MSR

(TEMP_BASE_MSR)

TSS Segment Base/Limit MSR

(TSS_BASE_MSR)

IDT Segment Base/Limit MSR (IDT_BASE_MSR)

GDT Segment Base/Limit MSR

(GDT_BASE_MSR)

SMM Segment Base/Limit MSR

(SMM_BASE_MSR

DMM Segment Base/ Limit MSR

(DMM_BASE_MSR)

Debug Registers 1 and 0 MSR (DR1_DR0_MSR)

Debug Registers 3 and 2 MSR (DR3_DR2_MSR)

Debug Registers 7 and 6 MSR (DR6_DR7_MSR)

Extended Debug Registers 1 and 0 MSR

(XDR1_XDR0_MSR)

Extended Debug Registers 3 and 2 MSR

(XDR3_XDR2_MSR)

Extended Debug Registers 5 and 4 MSR

(XDR5_XDR4_MSR)

00001353h

R/W

Extended Debug Registers 7 and 6 MSR

(XDR7_XDR6_MSR)

xxxxxxxx_xxxxxxxxh

Extended Debug Registers 9 and 8 MSR

(XDR9_XDR8_MSR)

Extended Debug Registers 11 and 10 MSR

(XDR11_XDR10_MSR)

EX Stage Instruction Pointer MSR (EX_IP_MSR)

WB Stage Instruction Pointer MSR (WB_IP_MSR)

EX Stage Linear Instruction Pointer MSR

(EX_LIP_MSR)

WB Stage Linear Instruction Pointer MSR

(WB_LIP_MSR)

C1/C0 Linear Instruction Pointer MSR

(C1_C0_LIP_MSR)

C3/C2 Linear Instruction Pointer MSR

(C3_C2_LIP_MSR)

Floating Point Environment Code Segment

(FPENV_CS_MSR)

Floating Point Environment Instruction Pointer

(FPENV_IP_MSR)

Floating Point Environment Data Segment

(FPENV_DS_MSR)

Floating Point Environment Data Pointer

(FPENV_DP_MSR)

Table 5-13. CPU Core Specific MSRs Summary (Continued)

MSR

Address

Type

Register Name

Reset Value

Reference