Table 6-68, Management interface phy address register, Table 6-69 – Artesyn ATCA-7470 Installation and Use (October 2014) User Manual

Page 193: Maps and registers

Maps and Registers

ATCA-7470 Installation and Use (6806800P15K)

193

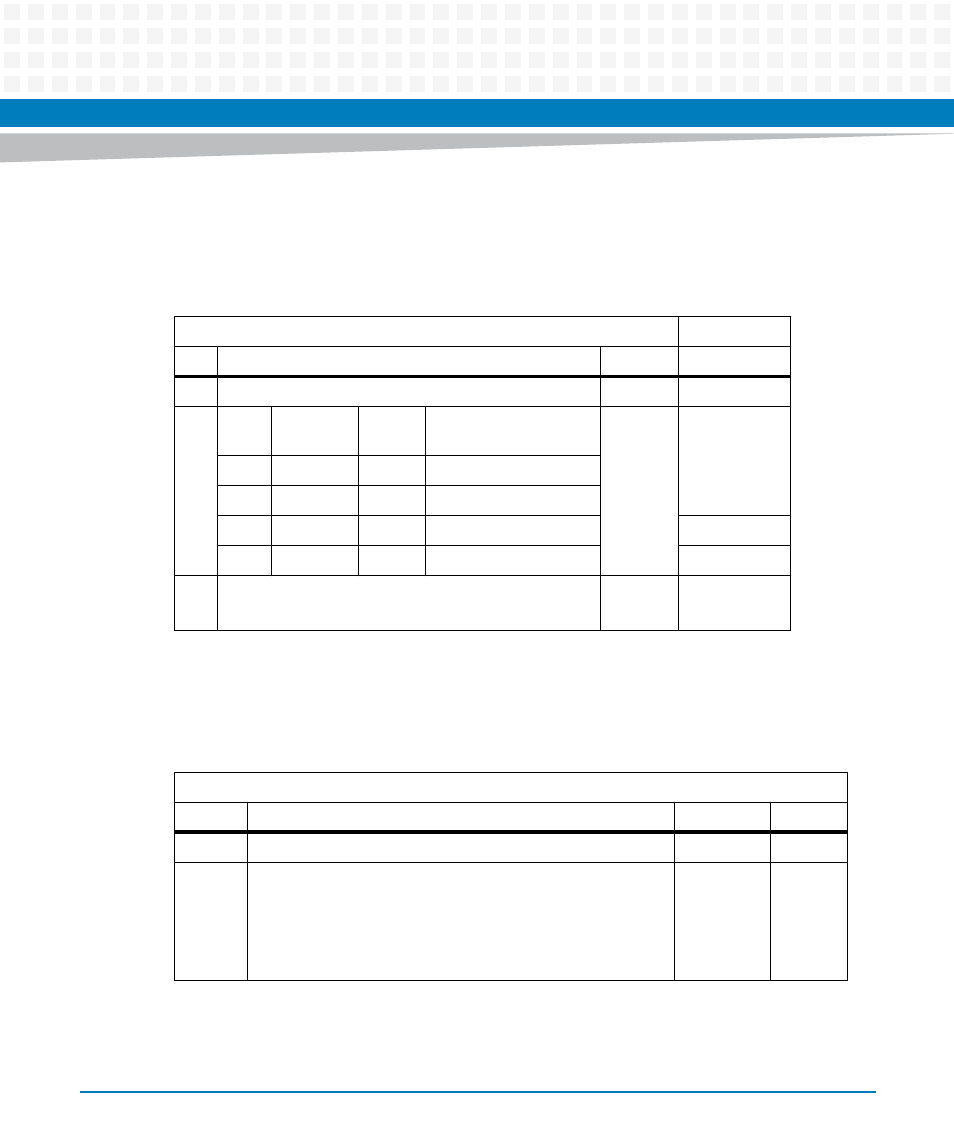

6.4.27 Serial Management Interface (MII) Control Registers

A write access to MII Management Interface Control and Address Register starts an MII

Management Interface operation.

Table 6-68 Management interface PHY Address Register

Address Offset: 0x70

Bit

Description

Default

Access

4:0

PHY Address

0

LPC: r/w

6:5

[6:5]

Divider

MDC

period

MDC Frequency

0

LPC: r/w

00

4

120 ns

8.333 MHz

01

8

240 ns

4.166 MHz

10

16

480 ns

2.083 MHz

11

32

960 ns

1.046 MHz

7

0: MII disabled. MDC and MDIO are always tristated.

1: MII enabled. A write to the bit starts an operation.

0

LPC: r/w

Table 6-69 MII Management Interface Control and Address Register

Address Offset: 0x71

Bit

Description

Default

Access

4:0

Internal PHY (Switch) register address

0

LPC: r/w

5

Turnaround status bit. The bit is set/reset after a MDIO read

operation.

0: A target device has driven MDIO low during 2nd TA bit

(normal operation)

1: No device has responded to the read operation

0

LPC:

r/w1c