3 telecom clock monitor registers, Table 6-59, Supervised telecom clocks reference list – Artesyn ATCA-7470 Installation and Use (October 2014) User Manual

Page 188: Table 6-60, Telecom clock monitor control register, Table 6-61, Telecom clock monitor status register, Maps and registers

Maps and Registers

ATCA-7470 Installation and Use (6806800P15K)

188

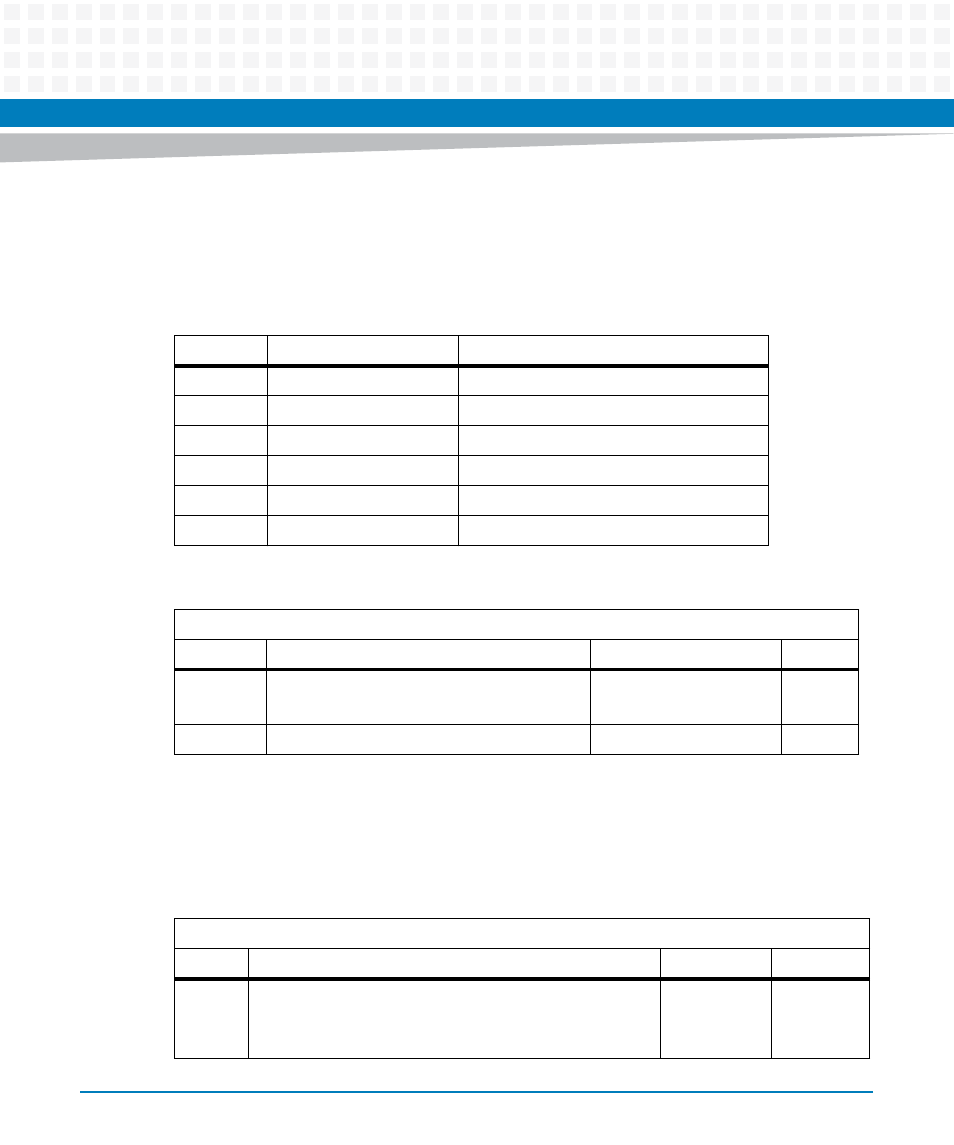

6.4.26.3 Telecom Clock Monitor Registers

All incoming telecom clocks can be monitored and measured in the range from 1 Hz to 166

MHz. Up to 5 different clock inputs may be monitored.

When at least one bit of the

Table "Telecom Clock Monitor Status Register" on page 188

is set,

the corresponding status bit CLK_MONITOR_FINISHED of the

Control/Status Register" on page 167

is also set.

Table 6-59 Supervised Telecom Clocks Reference List

Number

Name

Description

0

LCCB_SYSCLK_IN_A

CLK2A from backplane

1

LCCB_SYSCLK_IN_B

CLK2B from backplane

2

LCCB_FPETH_RCLK1

Recovered PHY clock 1

3

LCCB_FPETH_RCLK2

Recovered PHY clock 2

4

LCCB_FRSYNC

Clock FRSYNC from ACS8525

5 - 7

-

Reserved

Table 6-60 Telecom Clock Monitor Control Register

Address: 0x61

Bit

Description

Default

Access

4:0

Enable supervised Telecom Clock 0 to 4

Set corresponding bit enable monitoring.

PWR_GOOD: 0

LPC: r/w

7:5

Reserved

0

r

Table 6-61 Telecom Clock Monitor Status Register

Address: 0x62

Bit

Description

Default

Access

4:0

Result available for supervised Telecom Clock 0 to 4.

Corresponding bit is set when measurement has finished.

Clearing bit triggers new measurement.

0

LPC: r/w1c