10 software reset register, 11 fwh_pltrst_ enable register, 11 interrupt control and status registers – Artesyn ATCA-7470 Installation and Use (October 2014) User Manual

Page 165: Table 6-28, Software reset control register, Table 6-29, Fwh_pltrst_ reset enable register, Maps and registers

Maps and Registers

ATCA-7470 Installation and Use (6806800P15K)

165

6.4.10.10 Software Reset Register

The Register depicts the functionality of CF9 register of PCH. Bit 2 controls the software reset.

Writing 1 to bit# 2 of this register generates a reset signal. Depending upon the ADR enable bit,

the reset is generated immediately or delayed after ADR. Bit#2 is automatically reset to zero in

next clock cycle.

6.4.10.11 FWH_PLTRST_ Enable Register

By default the FWH_PLTRST_ Reset is disabled. BIOS enables this reset output by writing bit 0

of this register. IPMI has only read access to the register. OS should not modify this register.

Once enabled, the FWH_PLTRST_ is directly connected to the PCH_PLTRST.

6.4.11 Interrupt Control and Status Registers

The interrupt status registers indicate the status of the interrupt input signals. They are read

only registers. When an interrupt is active the corresponding status bit is read 1. Write access

to these register bits does not have any impact.

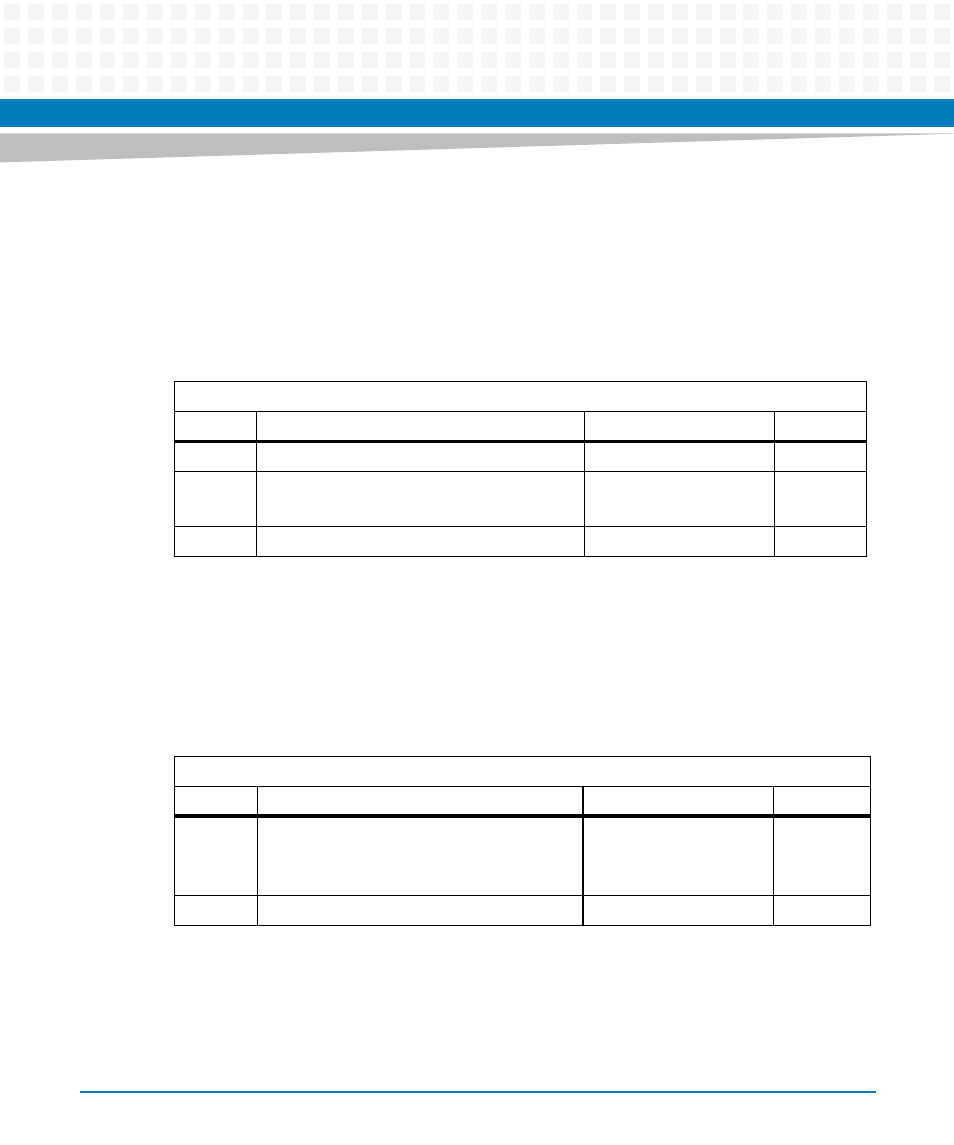

Table 6-28 Software Reset Control Register

Address Offset: 0x19

Bit

Description

Default

Access

1:0

Reserved 0

r

2

Setting this bit generates PCH_SYS_RST_

The bit is automatically set to 0 upon reset.

0

LPC: w

IPMC: w

7:3

Reserved 0

r

Table 6-29 FWH_PLTRST_ Reset Enable Register

Address Offset: 0x1B

Bit

Description

Default

Access

0

Mask bit for FWH_PLTRST_ (LPC/KCS) reset

0: FWH_PLTRST_ is driven low

1: FWH_PLTRST_ is driven by PCH_PLTRST_

PWR_GOOD:0

LPC: r/w

IPMC: r

7:1

Reserved 0

r