25 miscellaneous status/control registers, Table 6-53, Misc (ethernet link and cpu error) status register – Artesyn ATCA-7470 Installation and Use (October 2014) User Manual

Page 184: Maps and registers

Maps and Registers

ATCA-7470 Installation and Use (6806800P15K)

184

6.4.25 Miscellaneous Status/Control Registers

1

Base interface 2 link status (Status of BASEIF2_LINKLOSS signal)

0:Link established

1:Link is down

Ext.

r

7:2

Reserved

0

r

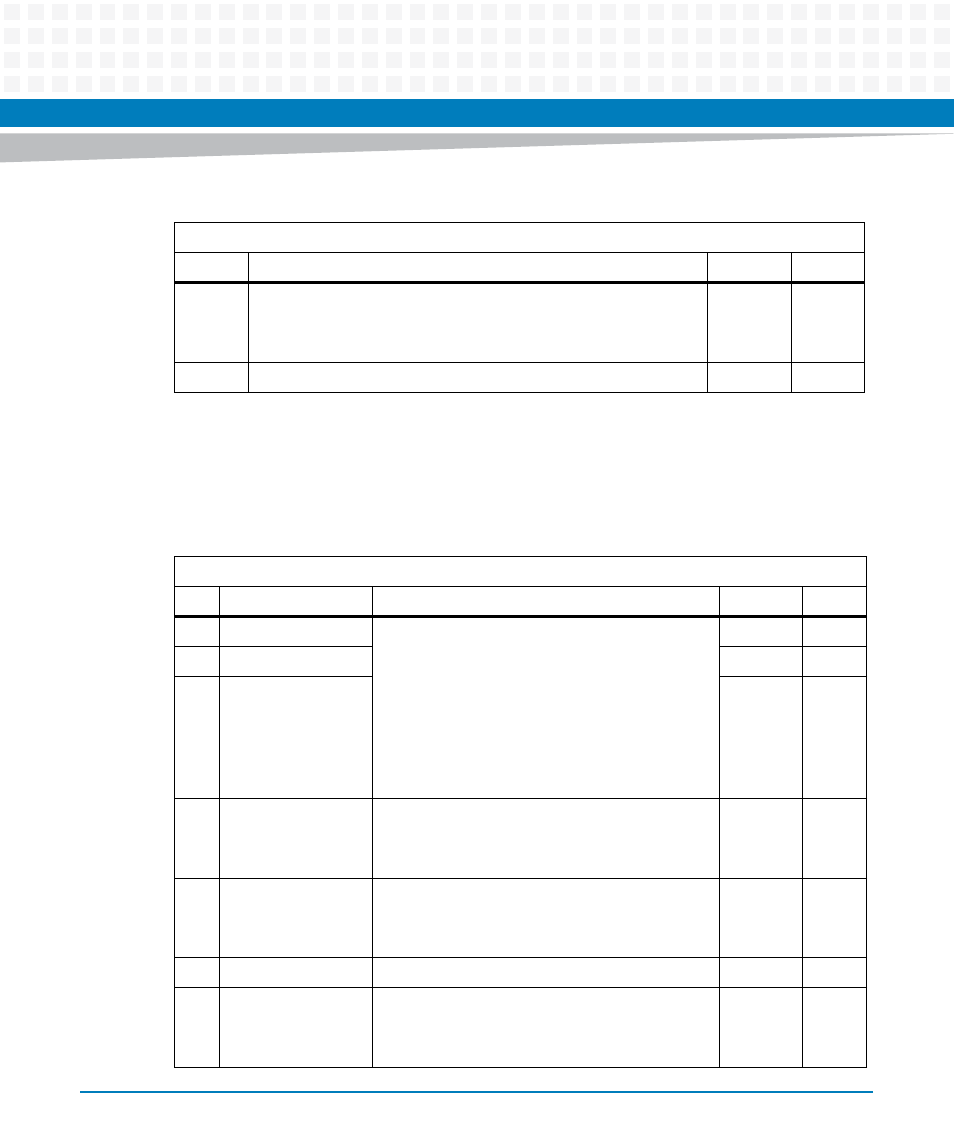

Table 6-52 Base Interface Link Status Signals Register

Address Offset: 0x56

Bit

Description

Default

Access

Table 6-53 Misc (Ethernet Link and CPU Error) Status Register

Address Offset: 0x57

Bit

Signal

Description

Default

Access

0

FM_ERR_[0[

Error status signals from Sandybridge-EP CPUs to

Cavecreek.

Bit 0 = Hardware correctable error (no operating

system or firmware action required)

Bit 1 = Non-fatal error (operating system or

firmware action required to contain and recover)

Bit 2 = Fatal error (system reset likely required to

recover)

Ext.

r

1

FM_ERR_[1]

Ext.

r

2

FM_ERR_[2]

Ext.

r

3

PCH0_PCIE_WIDTH

PCH PCIE interface status

0: PCIE x4 to RTM port 6

1: PCIE x1 to VGA

Ext.

r

4

FPGA_PROM_SEL

FPGA PROM select signal controlled by IPMC

0: FPGA connected to recovery PROM

1: FPGA connected to default PROM

Ext.

r

5

IPMC_GPIO1

GPIO1 signal from IPMC

Ext.

r

6

ACC_MOD_PRSNT_ ACC module present signal

0: ACC module not present. Signal high.

1: ACC module present. Signal low.

Ext.

r