5 interrupt mask and map registers, Table 6-33, Address map of interrupt mask and map registers – Artesyn ATCA-7470 Installation and Use (October 2014) User Manual

Page 168: Maps and registers

Maps and Registers

ATCA-7470 Installation and Use (6806800P15K)

168

6.4.11.5 Interrupt Mask and Map Registers

Interrupts from different interrupt sources including the External Interrupt sources can be

mapped to one of the CPU_IRQ_X_ interrupt or any IRQ Frame number of the serialized IRQ

protocol.

Multiple interrupt sources may share the same CPU_IRQ_X_ or the same IRQ Frame. In this

case all interrupt sources need to be of type "level active low".

Each Interrupt source has an Interrupt Mask and Map Register. See the

Interrupt Mask and Map Registers" on page 168

.

2

Telecom interrupt Event 2:

Reflects Interrupt signal LCCB_INTREQ_ from ACS

telecom clock device:

0: not asserted. High

1: asserted. Low

Ext.

LPC: r

3

Reserved

0

r

6: 4

Enable for Telecom interrupt events 0 to 2:

0: interrupt is disabled

1: Interrupt is enabled

0

LPC: r/r

7

Reserved

0

r

Table 6-32 Telecom Interrupt Control/Status Register (continued)

Address Offset: 0x22

Bit

Description

Default

Access

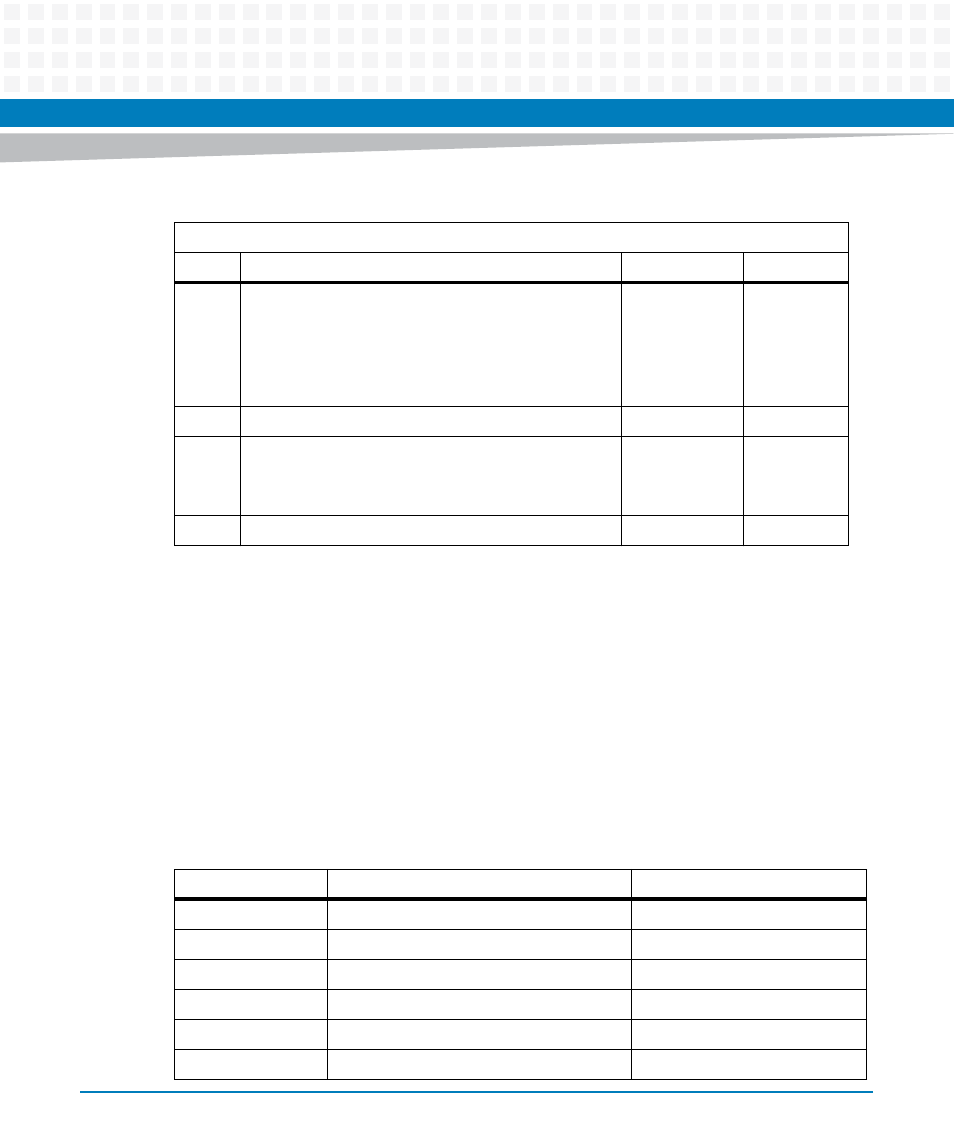

Table 6-33 Address Map of Interrupt Mask and Map Registers

Interrupt Source

Description

Address Offset of Interrupt Mask

IPMC2HOST_INT_

IPMC signals interrupt

0x23

LM75_INT_

Interrupt input from payload Temp sensor

0x24

ETH_BASE_INT_

IRQ request from 88E6161 Marvell Switch

0x25

ETH_FP_INT_

IRQ request from 88E1322 Marvell PHY

0x26

THERM_ALERT_

IRQ request from IOH Thermo-sensor

0x27

APB_ALARM

An 48V input alarm (low voltage, etc)

0x28