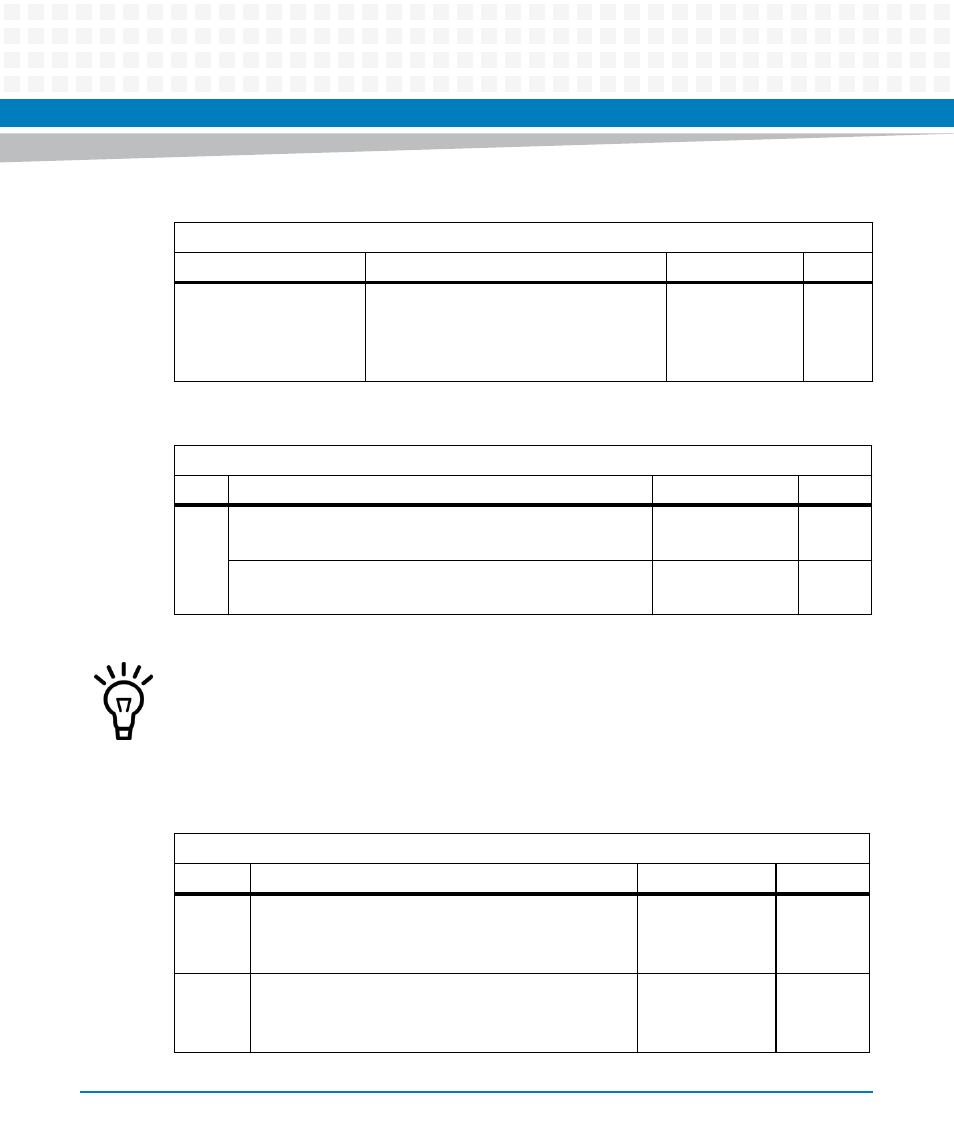

Table 6-56, Acs8225b spi access data register, Table 6-57 – Artesyn ATCA-7470 Installation and Use (October 2014) User Manual

Page 186: Acs8225b status/control register, Maps and registers

Maps and Registers

ATCA-7470 Installation and Use (6806800P15K)

186

7

SPI Busy Bit:

0: Ready for next read or write access

1: Busy. The SPI clock is still toggling Or SPI

owned by FSM

CPU_PWROK: 0

LPC: r

Table 6-56 ACS8225B SPI Access Data Register

Address Offset: 0x5E

Bit

Description

Default

Access

7:0

ACS8525B write data register

Write data before SPI address and command written

-

LPC: r/w

ACS8525B read data register

Contains read data after SPI address and command written

CPU_PWROK: 0

LPC: r

Table 6-55 ACS8225B SPI Status Register (continued)

Address Offset: 0x5D

Bit

Description

Default

Access

SP should read or write to the XACS8225B SPI Access RegisterX only when Busy Bit in

ACS8225B SPI Status Register is not set.

Table 6-57 ACS8225B Status/Control Register

Address Offset: 0x5F

Bit

Description

Default

Access

0

Control ACS SRCSW signal:

0: drive LCCB_SRCSW low

1: drive LCCB_SRCSW high

CPU_PWROK: 0

LPC: r/w

1

Control ACS_PORST# signal:

0: No action

1: drive LCCB_RST_ low for one clock cycle

0

LPC: w1c