Altera DisplayPort MegaCore Function User Manual

Page 81

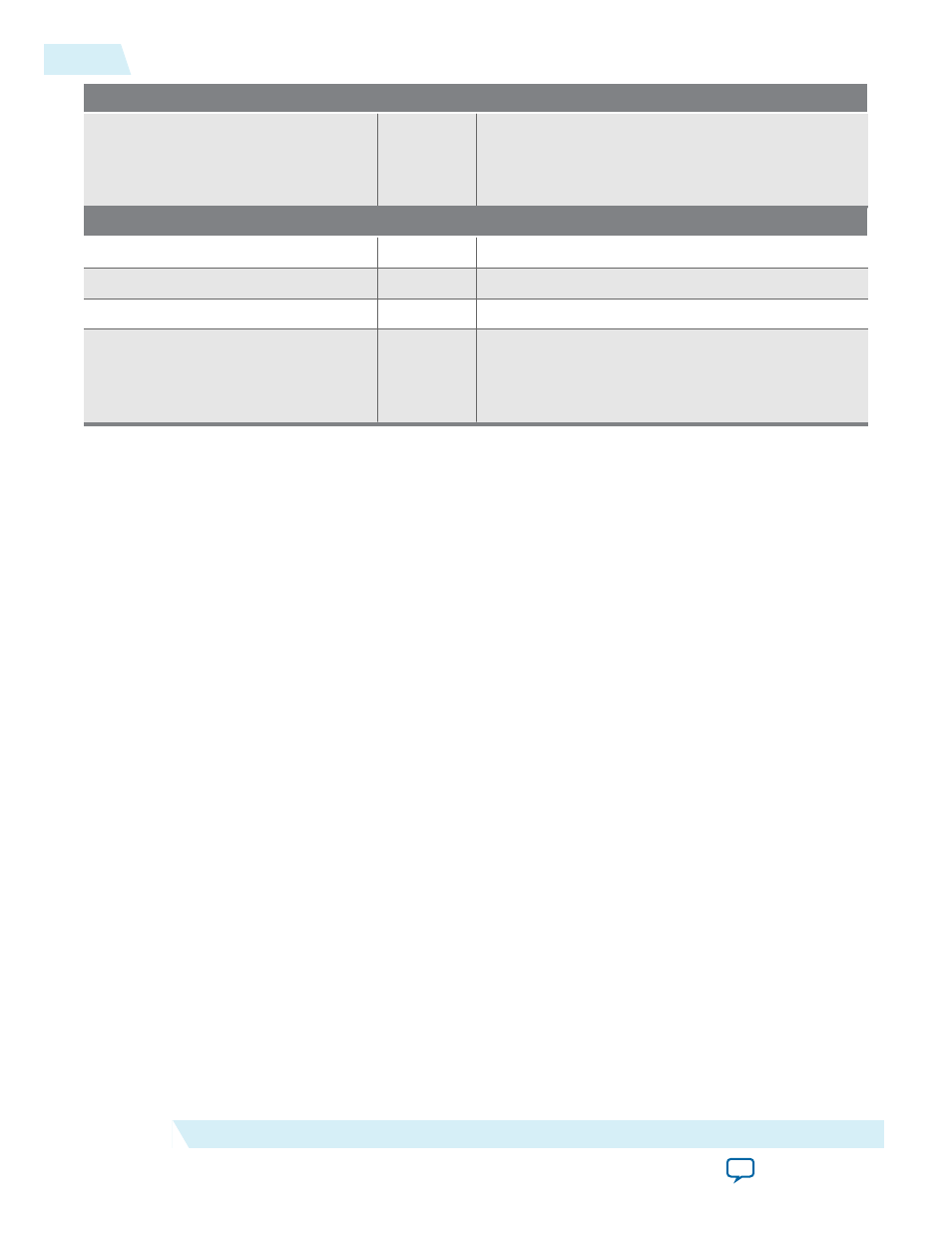

DP RX Connector J1

PWR_OUT

Output

DP_PWR

3.3V @ 500mA for sink-side cable adapter.

A standard DisplayPort cable must have no wire for

this pin.

DP RX Connector J2

CONFIG1

Input

Cable Adapter Detect for dual mode support.

CONFIG2

Not used

—

RTN_PWR

Input

Return signal for

DP_PWR

.

PWR_OUT

Output

DP_PWR

3.3V @ 500mA for source-side cable

adapter.

A standard DP cable must have no wire for this pin.

Example 6-1: Main Link Re-driver Programming Example

Bitec DP daughter card has Main Link redriver (SN75DP130) that boosts link performance. In

typical applications, the redriver EQ, VOD/pre-emphasis levels can be set automatically based on

link training. In some cases, you may want to manually configure the settings. The following is an

example code that manually configures the redriver EQ, VOD/Pre-emphasis settings.

Note: The bitec_i2c_write() function is called inside

main.c

in the demonstration

software. I

2

C address 0×58 is the write address for the RX redriver.

//*********************************************************

// Disable link training (DP130 reg=0×04, data=0×00)

//*********************************************************

// Disable DP130 link training to enable I2C programming

bitec_i2c_write(0×58, 0×04, 0×00);

//*********************************************************

// Program link bandwidth settings to HBR2 (DPCD addr=0×00100, data=0×14)

//*********************************************************

bitec_i2c_write(0×58, 0×1c, 0×00); // DPCD addr[19:16]=0×0

bitec_i2c_write(0×58, 0×1d, 0×01); // DPCD addr[15:8]=0×01

bitec_i2c_write(0×58, 0×1e, 0×00); // DPCD add[7:0]=0×00

bitec_i2c_write(0×58, 0×1f, 0×14); // DPCD data=0×14

//*********************************************************

// Program lane count to 4 (DPCD addr=0x00101, data=0x4)

//*********************************************************

bitec_i2c_write(0×58, 0×1c, 0×00); // DPCD addr[19:16]=0×0

bitec_i2c_write(0×58, 0×1d, 0×01); // DPCD addr[15:8]=0×01

bitec_i2c_write(0×58, 0×1e, 0×01); // DPCD addr[7:0]=0×01

bitec_i2c_write(0×58, 0×1f, 0×04); // DPCD data=0×4

//*********************************************************

// Program VOD Level 1 and Pre-emphasis Level 0 for lane 0

// (DPCD addr=0×00103, data=0×01)

//*********************************************************

bitec_i2c_write(0×58, 0×1c, 0×00); // DPCD addr[19:16]=0×0

bitec_i2c_write(0×58, 0×1d, 0×01); // DPCD addr[15:8]=0×01

bitec_i2c_write(0×58, 0×1e, 0×03); // DPCD addr[7:0]=0×03

bitec_i2c_write(0×58, 0×1f, 0×01); // DPCD data=0×01

6-20

Required Hardware

UG-01131

2015.05.04

Altera Corporation

DisplayPort IP Core Hardware Demonstration