Source audio registers, Source audio registers -12 – Altera DisplayPort MegaCore Function User Manual

Page 133

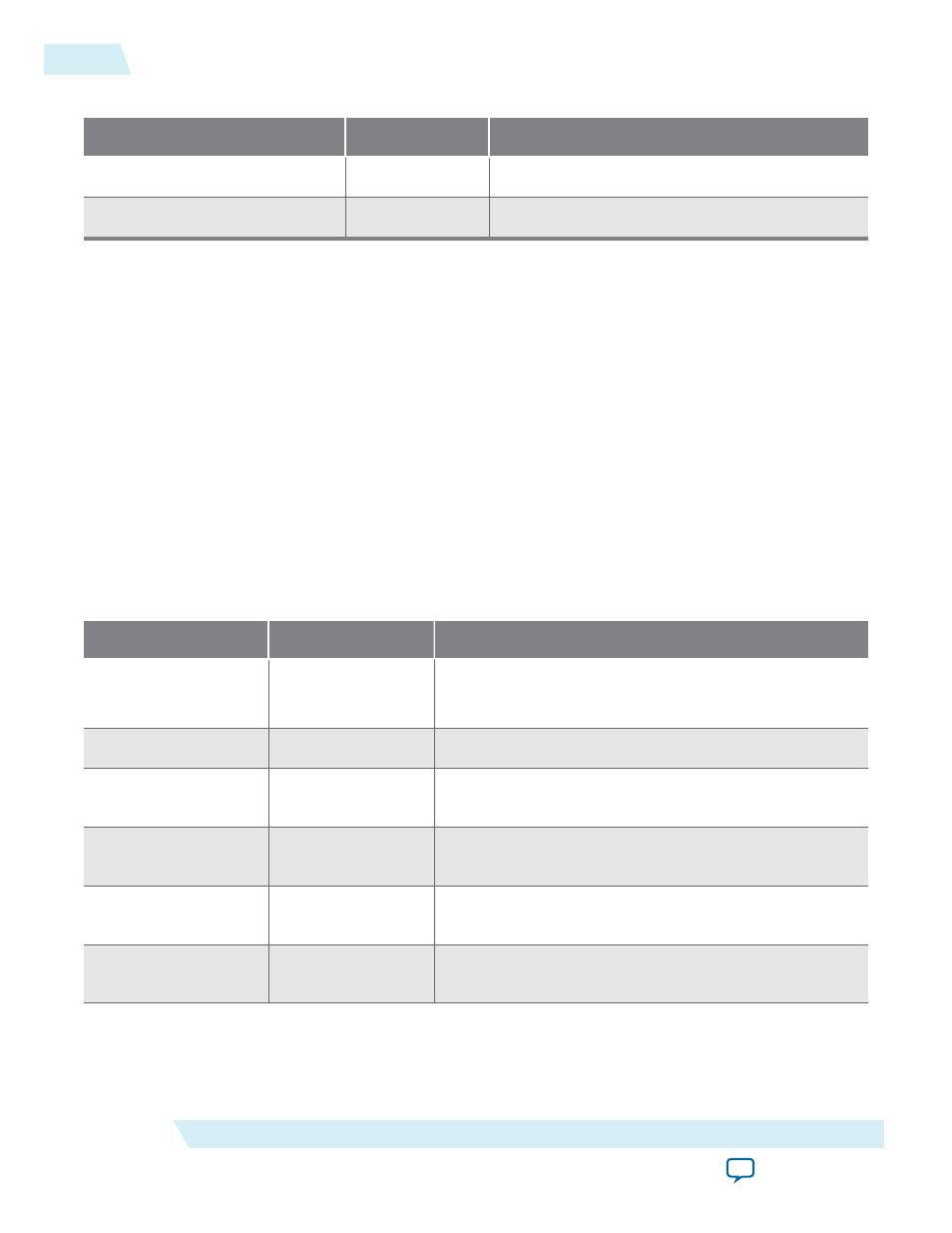

Table 9-24: DPTX_TIMESTAMP Bits

Bit

Bit Name

Function

31:24

Unused

8’b00000000

23:0

TIMESTAMP

Free-running counter value (1 tick equals 100 µs)

Source Audio Registers

The Audio registers are allocated at addresses:

• 0×002f for Stream 0

• 0×004f for Stream 1

• 0×006f for Stream 2

• 0×008f for Stream 3

Note: Only registers for Stream 0 are listed in the following sections.

The following register controls the values related to the audio data stream 0.

Address: 0×002f

Direction: RW

Reset: The maximum number of channels supported minus 1 0×00000000 to 0×00000007

Table 9-25: DPTX0_AUD_CONTROL Bits

Bit

Bit Name

Function

31

SOFT_MUTE

1 = Audio is muted

0 = Audio is muted if

tx_audio_mute

is asserted

30:24

Unused

17:16

LFEBPL

Audio InfoFrame LFE playback level (LFEPBL, see CEA-

861-E specification)

15:8

CA

Audio InfoFrame channel allocation (CA, see CEA-861-E

specification)

7:4

LSV

Audio InfoFrame level shift value (LSV, see CEA-861-E

specification)

3

DM_INH

Audio InfoFrame down mix inhibit flag (DM_INH, see

CEA-861-E specification)

9-12

Source Audio Registers

UG-01131

2015.05.04

Altera Corporation

DisplayPort Source Register Map and DPCD Locations