Dptx_reconfig, Source timestamp, Dptx_reconfig -11 – Altera DisplayPort MegaCore Function User Manual

Page 132: Source timestamp -11

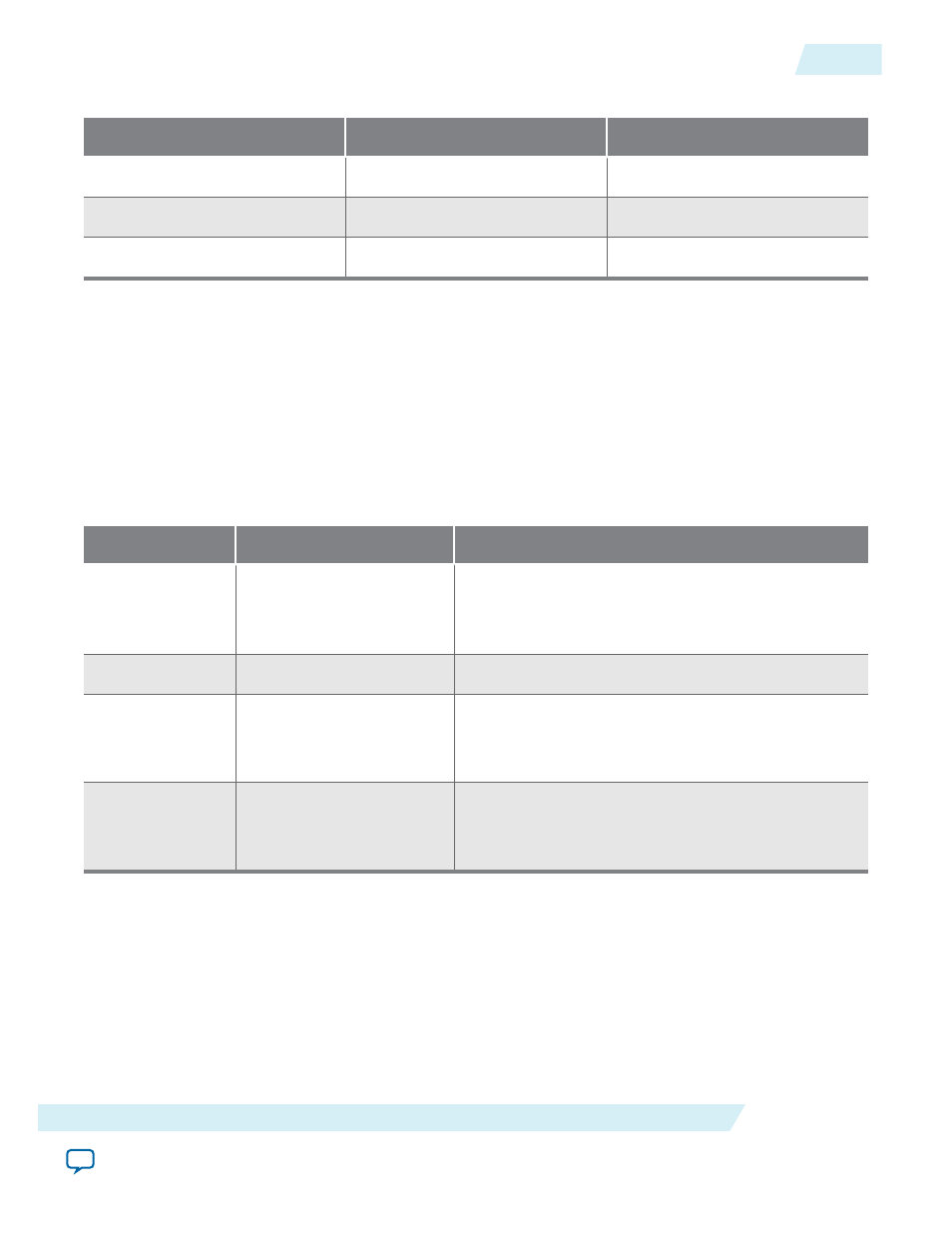

Table 9-22: DPTX_PRE_VOLT3 Bits

Bit

Bit Name

Function

31:4

Unused

3:2

PRE3

Pre-emphasis output on lane 3

1:0

VOLT3

Voltage swing output on lane 3

DPTX_RECONFIG

RECONFIG_ANALOG

drives the

tx_analog_reconfig

port (

tx_analog_reconfig_req

) , while

RECONFIG_LINKRATE

drives the

tx_reconfig

port,

(tx_reconfig_req

) .

GXB_BUSY

connects to the

tx_analog_reconfig

input ports (

tx_analog_reconfig_busy

, and

tx_reconfig tx_reconfig_busy

).

Address: 0×0014

Direction: RW

Reset: 0×00000000

Table 9-23: DPTX_RECONFIG Bits

Bit

Bit Name

Function

31

GXB_BUSY

Read-only flag where:

• 0 = Transceiver is not busy

• 1 = Transceiver is busy

30:2

Unused

1

RECONFIG_LINKRATE

This flag always reads back at 0.

1 = Reconfigure the transceiver with the link rate in

DPTX_TX_CONTROL

(

TX_LINK_RATE

)

0

RECONFIG_ANALOG

This flag always reads back at 0.

1 = Reconfigure transceiver with analog values in

DPTX_PRE_VOLT0-3

Source Timestamp

The Nios II processor can use this global, free-running counter to generate timestamps and delays. The

same counter is used in both sink and source instantiations (

DPRX_TIMESTAMP

is always equal to

DPTX_TIMESTAMP

).

Address: 0×001F

Direction: RO

Reset: 0×00000000

UG-01131

2015.05.04

DPTX_RECONFIG

9-11

DisplayPort Source Register Map and DPCD Locations

Altera Corporation