Clock recovery interface, Clock recovery interface -6 – Altera DisplayPort MegaCore Function User Manual

Page 67

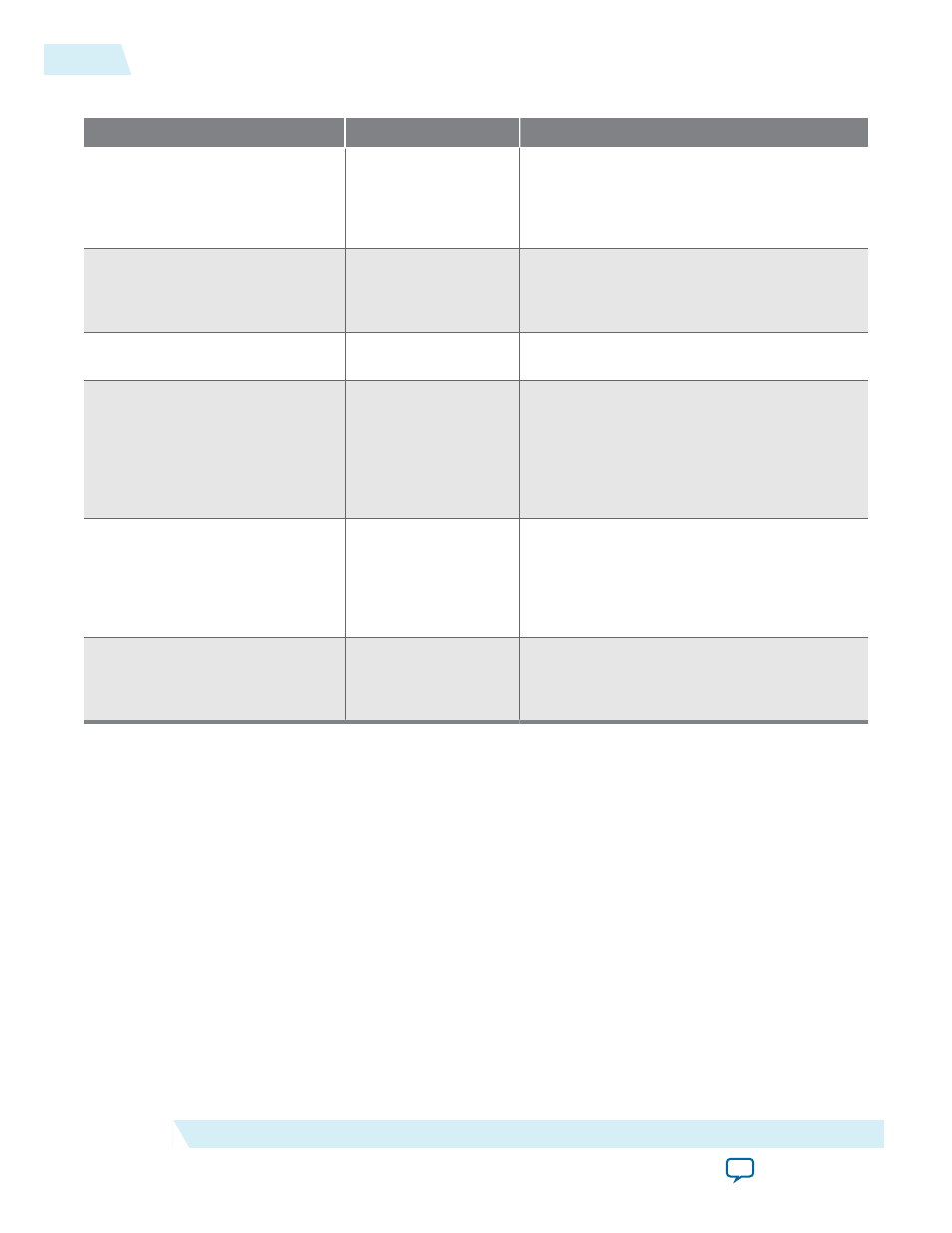

Table 6-2: Clock Recovery Core Parameters

Parameter

Default Value

Description

SYMBOLS_PER_CLOCK

4

Specifies the configuration of the DisplayPort

RX transceiver used.

Set to 2 for 20-bit mode (2 symbols per clock)

or to 4 for 40-bit mode (4 symbols per clock).

CLK_PERIOD_NS

10

Specifies the period (in nanoseconds) of the

clock signal connected to the port. Altera

recommends that you set about 60 MHz to

achieve timing closure.

DEVICE_FAMILY

Arria V

Identifies the family of the device used. The

values are Arria V, Stratix V, and Cyclone V.

FIXED_NVID

1*

Specifies the configuration of the DisplayPort

RX received video clocking used.

Set to 0 for synchronous clocking, where the

value of Nvid is variable. Set to 1 for

asynchronous clocking, where the Nvid value

is fixed to 32’h8000 (32,768).

PIXELS_PER_CLOCK

1

Specifies how many pixels in parallel (for

each clock cycle) are gathered from the

DisplayPort RX.

Set to 1 for single pixel, 2 for dual, or 4 for

four pixels per clock cycle.

BPP

24

Specifies the width (in bits) of a single pixel.

Set to 18 for 6-bit color, 24 for 8-bit color,

and so on up to 48 for 16-bit color.

Note: Most DisplayPort source devices transmit video using asynchronous clocking. For optimized

resource usage, Altera recommends you to set parameter FIXED_NVID to 1.

Clock Recovery Interface

The following table lists the signals for the clock recovery core.

6-6

Clock Recovery Interface

UG-01131

2015.05.04

Altera Corporation

DisplayPort IP Core Hardware Demonstration