Source-supported dpcd locations, Source-supported dpcd locations -29 – Altera DisplayPort MegaCore Function User Manual

Page 150

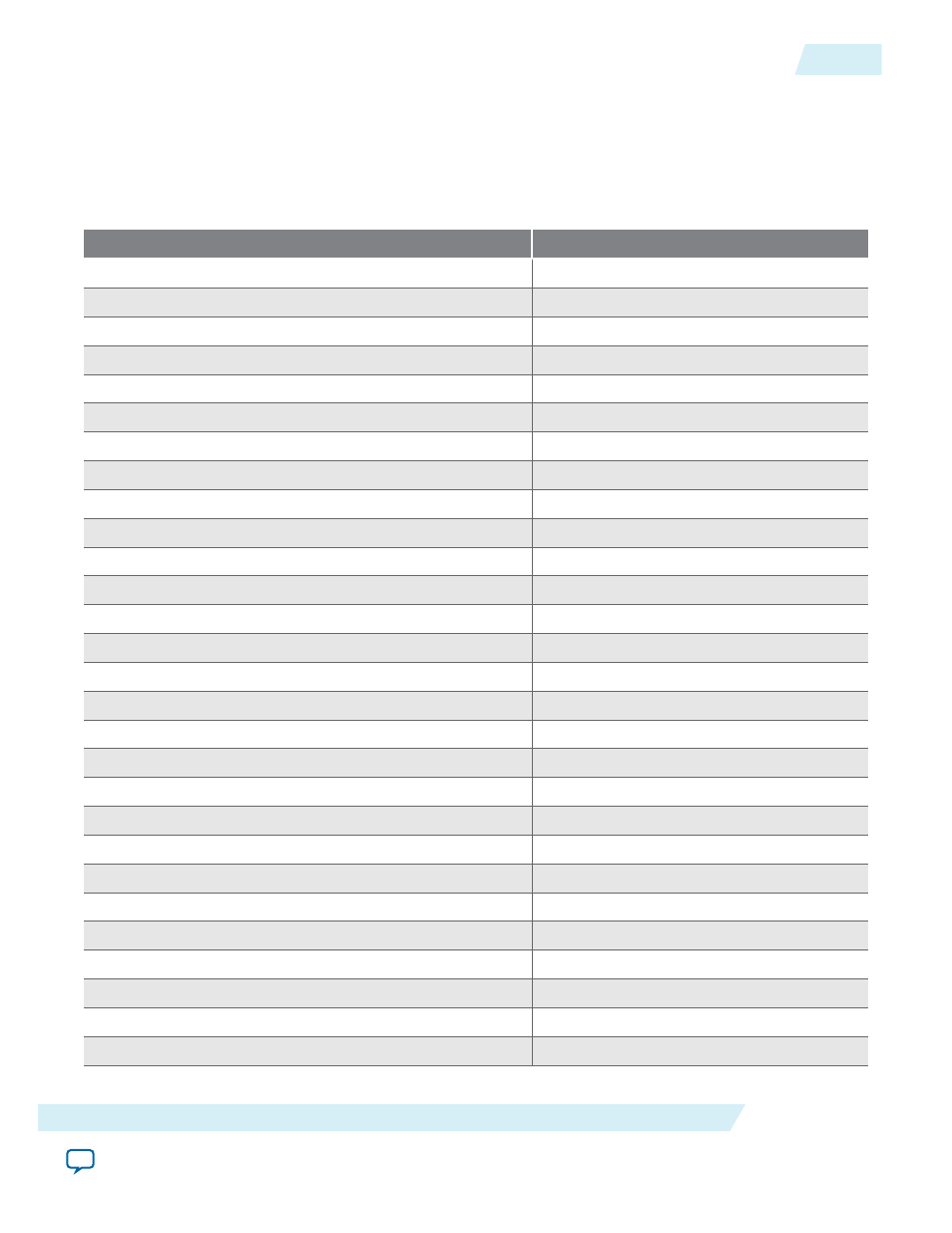

Source-Supported DPCD Locations

The following table describes the DPCD locations (or location groups) that are supported in DisplayPort

source instantiations.

Table 9-61: DPCD Locations

Location Name

Address

DPCD_REV

0×0000

MAX_LINK_RATE

0×0001

MAX_LANE_COUNT

0×0002

TRAINING_AUX_RD_INTERVAL

0×000E

MST_CAP

0×0021

GUID

0×0030

DPCP_ADDR_RX_GTC_VALUE7_0

0×0054

DPCP_ADDR_RX_GTC_VALUE15_8

0×0055

DPCP_ADDR_RX_GTC_VALUE23_16

0×0056

DPCP_ADDR_RX_GTC_VALUE31_24

0×0057

DPCP_ADDR_RX_GTC_MSTR_REQ

0×0058

DPCP_ADDR_RX_GTC_FREC_LOCK_DONE

0×0059

LINK_BW_SET

0×0100

LANE_COUNT_SET

0×0101

TRAINING_PATTERN_SET

0×0102

TRAINING_LANE0_SET

0×0103

TRAINING_LANE1_SET

0×0104

TRAINING_LANE2_SET

0×0105

TRAINING_LANE3_SET

0×0106

DOWNSPREAD_CTRL

0×0107

MSTM_CTRL

0×0111

DPCP_ADDR_TX_GTC_VALUE7_0

0×0154

DPCP_ADDR_TX_GTC_VALUE15_8

0×0155

DPCP_ADDR_TX_GTC_VALUE23_16

0×0156

DPCP_ADDR_TX_GTC_VALUE31_24

0×0157

DPCP_ADDR_RX_GTC_VALUE_PHASE_SKEW_EN

0×0158

DPCP_ADDR_TX_GTC_FREQ_LOCK_DONE

0×0159

PAYLOAD_ALLOCATE_SET

0×01C0

UG-01131

2015.05.04

Source-Supported DPCD Locations

9-29

DisplayPort Source Register Map and DPCD Locations

Altera Corporation