Dprx_mst_vcptab0, Dprx_mst_vcptab0 -17 – Altera DisplayPort MegaCore Function User Manual

Page 168

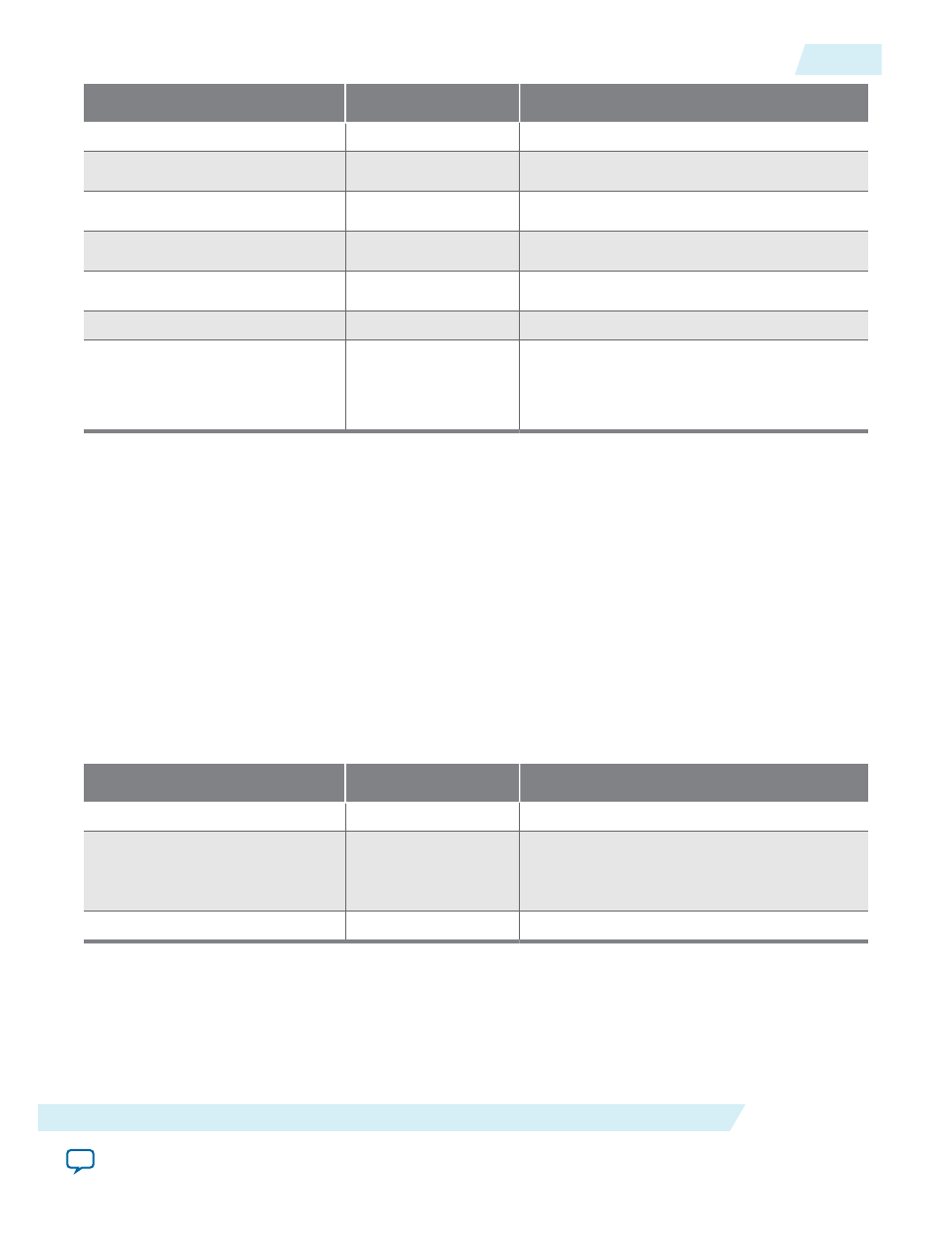

Bit

Bit Name

Function

29:20

Unused

19:16

VCP_ID3

VC payload ID for Stream 3

15:12

VCP_ID2

VC payload ID for Stream 2

11:8

VCP_ID1

VC payload ID for Stream 1

7:4

VCP_ID0

VC payload ID for Stream 0

3:1

Unused

0

MST_EN

Enable or disable MST

• 1 =MST framing

• 0 = SST framing

When you assert

VCPTAB_UPD_FORCE

, the sink forces the VC payload table contained in

DPRX_MST_VCPTAB0

through

DPRX_MST_VCPTAB7

to be taken immediately into use.

When you assert

VCPTAB_UPD_REQ

, the sink requests the VC payload table contained in

DPRX_MST_VCPTAB0

to

DPRX_MST_VCPTAB7

to be taken into use after the next ACT sequence is detected.

The VC Payload ID values (1–15) used for VCP_ID0 to VCP_ID3 are different from those used by the

DisplayPort source (1–63). The GPU must remap these values. The values used have to match those in the

VC Payload ID table—

DPRX_MST_VCPTAB0

to

DPRX_MST_VCPTAB7

registers.

MST controller status

Address: 0×00a1

Direction: RO

Reset: 0×00000000

Table 10-33: DPRX_MST_STATUS1 Bits

Bit

Bit Name

Function

31

Unused

30

VCPTAB_ACT_ACK

• 1 = ACT sequence detected and VC

payload updated

• 0 = No change to VC payload ID table

29:0

Unused

VCPTAB_ACT_ACK

resets to 0 when

VCPTAB_UPD_REQ

deasserted.

VCPTAB_ACT_ACK

is set to 1 if

VCPTAB_UPD_REQ

is asserted and the ACT sequence is detected, signalling that the table contained in

DPRX_MST_VCPTAB0

to

DPRX_MST_VCPTAB7

registers have been taken into use.

DPRX_MST_VCPTAB0

VC Payload ID Table

UG-01131

2015.05.04

DPRX_MST_VCPTAB0

10-17

DisplayPort Sink Register Map and DPCD Locations

Altera Corporation