Altera DisplayPort MegaCore Function User Manual

Page 64

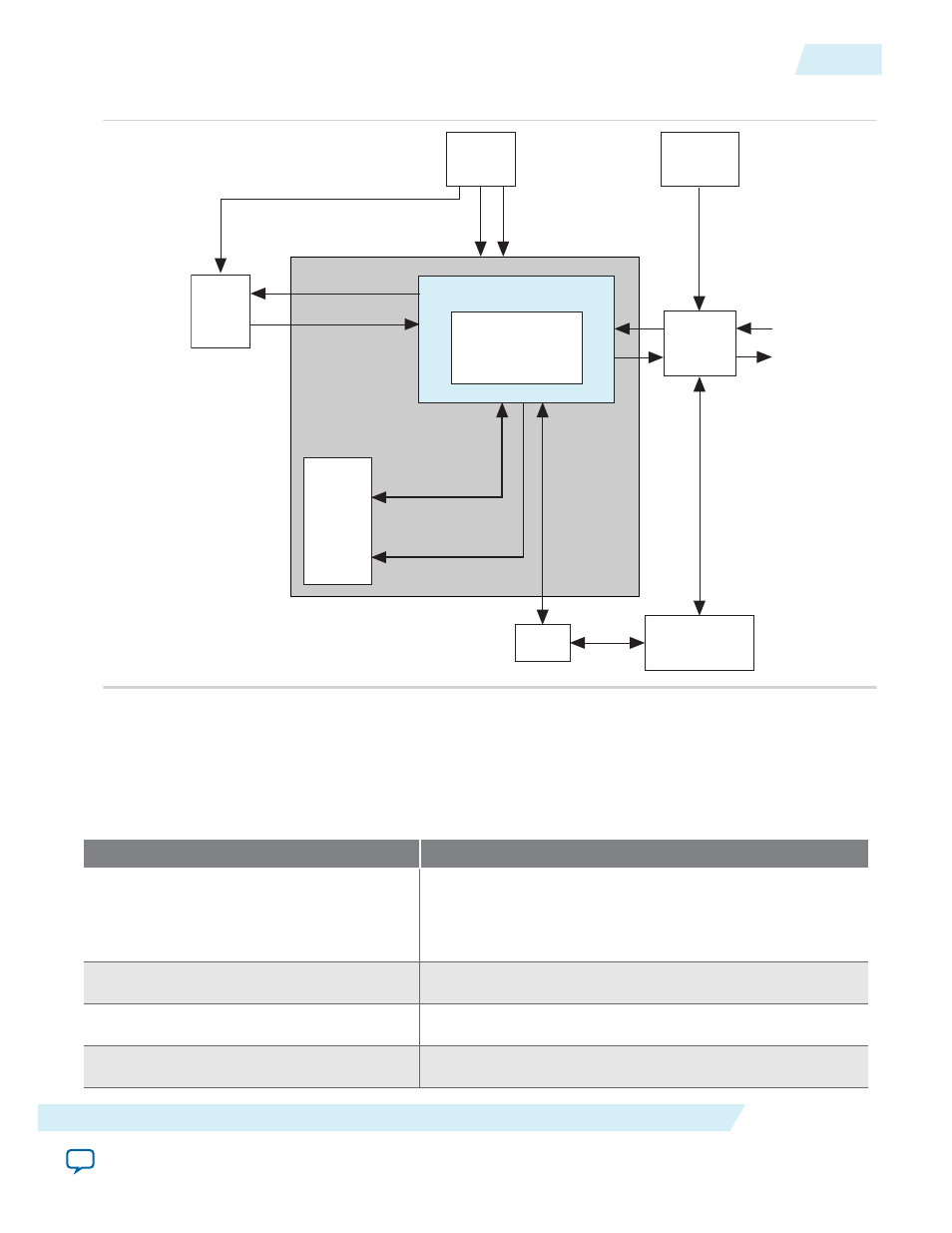

Figure 6-2: Hardware Demonstration Block Diagram

Nios II

Processor

Transceiver

Reconfiguration

RX

TX

DisplayPort IP Core

Bitec

DisplayPort Core

Qsys System (control .qsys)

Native

PHY

FSM

Management RX/TX

(Avalon-MM)

AUX Debug RX/TX

(Avalon-ST)

Transceiver

PLL

Video

PLL

Video Clock

160 MHz

AUX Clock

16 MHz

135 MHz

RX

TX

Clock

Recovery

RX

TX

Control Clock 60 MHz

During operation, you can adjust the DisplayPort source resolution (graphics card) from the PC and

observe the effect on the IP core. The Nios II software prints the source and sink AUX channel activity.

Press a push-button to print the current TX and RX MSAs.

Table 6-1: LED Function

The development board user LEDs illuminate to indicate the function described in the table below.

Arria V/Cyclone V/Stratix V/

Function

USER_LED[0]

This LED indicates that source is successfully lane-trained

and is sending video.

rxN_vid_locked

drives this LED.

This LED turns off if the source is not driving good video.

USER_LED[1]

This LED illuminates for 1-lane designs.

USER_LED[2]

This LED illuminates for 2-lane designs.

USER_LED[3]

This LED illuminates for 4-lane designs.

UG-01131

2015.05.04

DisplayPort IP Core Hardware Demonstration

6-3

DisplayPort IP Core Hardware Demonstration

Altera Corporation