Displayport sink, Sink overview, Sink functional description – Altera DisplayPort MegaCore Function User Manual

Page 37: Displayport sink -1, Sink overview -1, Sink functional description -1

DisplayPort Sink

5

2015.05.04

UG-01131

Sink Overview

The DisplayPort sink has a scalable main link with 1, 2, or 4 lanes for a total up to 21.6 Gbps bandwidth. A

bidirectional AUX channel with 1 Mbps Manchester encoding provides side-band communication. The

sink drives a hot plug detect (HPD) signal to notify the source that a sink is present. Additionally, it

provides an interrupt mechanism so that the sink can get the source’s attention.

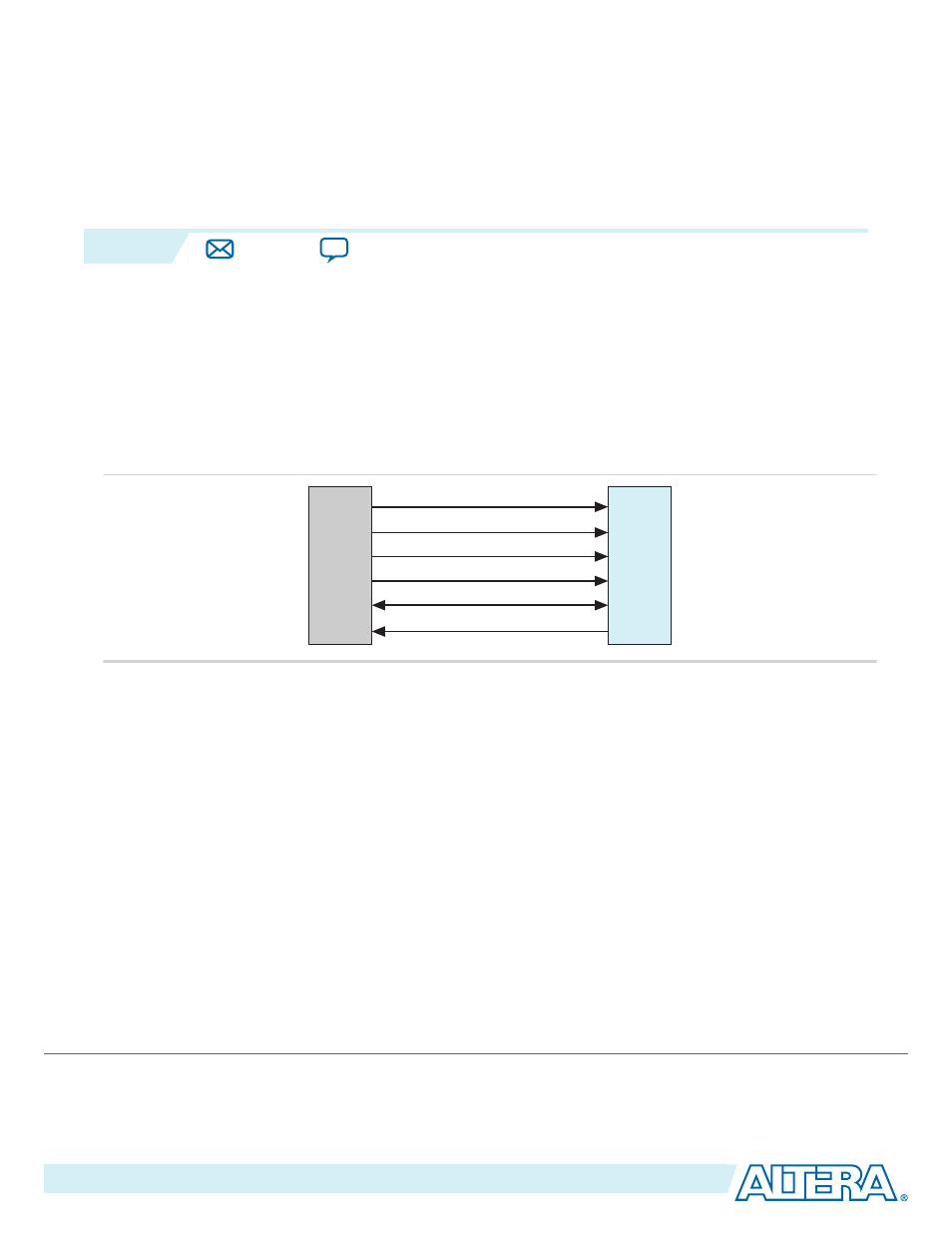

Figure 5-1: DisplayPort Sink Block Diagram

Source

Lane 0 Data (1.62, 2.7, or 5.4 Gbps)

Lane 1 Data (1.62, 2.7, or 5.4 Gbps)

Lane 2 Data (1.62, 2.7, or 5.4 Gbps)

Lane 3 Data (1.62, 2.7, or 5.4 Gbps)

AUX Channel (1 Mbps)

Hot Plug Detect

Sink

The main link has three selectable data rates: 1.62, 2.7, and 5.4 Gbps. The source device sets the lane count

and link rate combination (referred to as the policy) according to the sink’s capabilities and required

video bandwidth.

The AUX channel is an AC-coupled differential pair for bidirectional communication. The signaling is a

self-clocked Manchester encoding at 1 Mbps. Like 100-T Ethernet, the encoder uses a preceding synchro‐

nization pattern in each 16-byte maximum packet. The AUX channel uses a master/slave hierarchy in

which the source (master) initiates all communication.

Sink Functional Description

The DisplayPort sink has a complete set of parameters for optimizing device resources.

The DisplayPort sink consists of a DisplayPort decoder block, a transceiver management block, and a

controller interface block with an Avalon-MM interface for connecting with an embedded controller such

as the Nios II processor. You can configure the ports using an RTL wrapper instantiation or

implementing the IP core as a Qsys component.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134