Altera DisplayPort MegaCore Function User Manual

Page 48

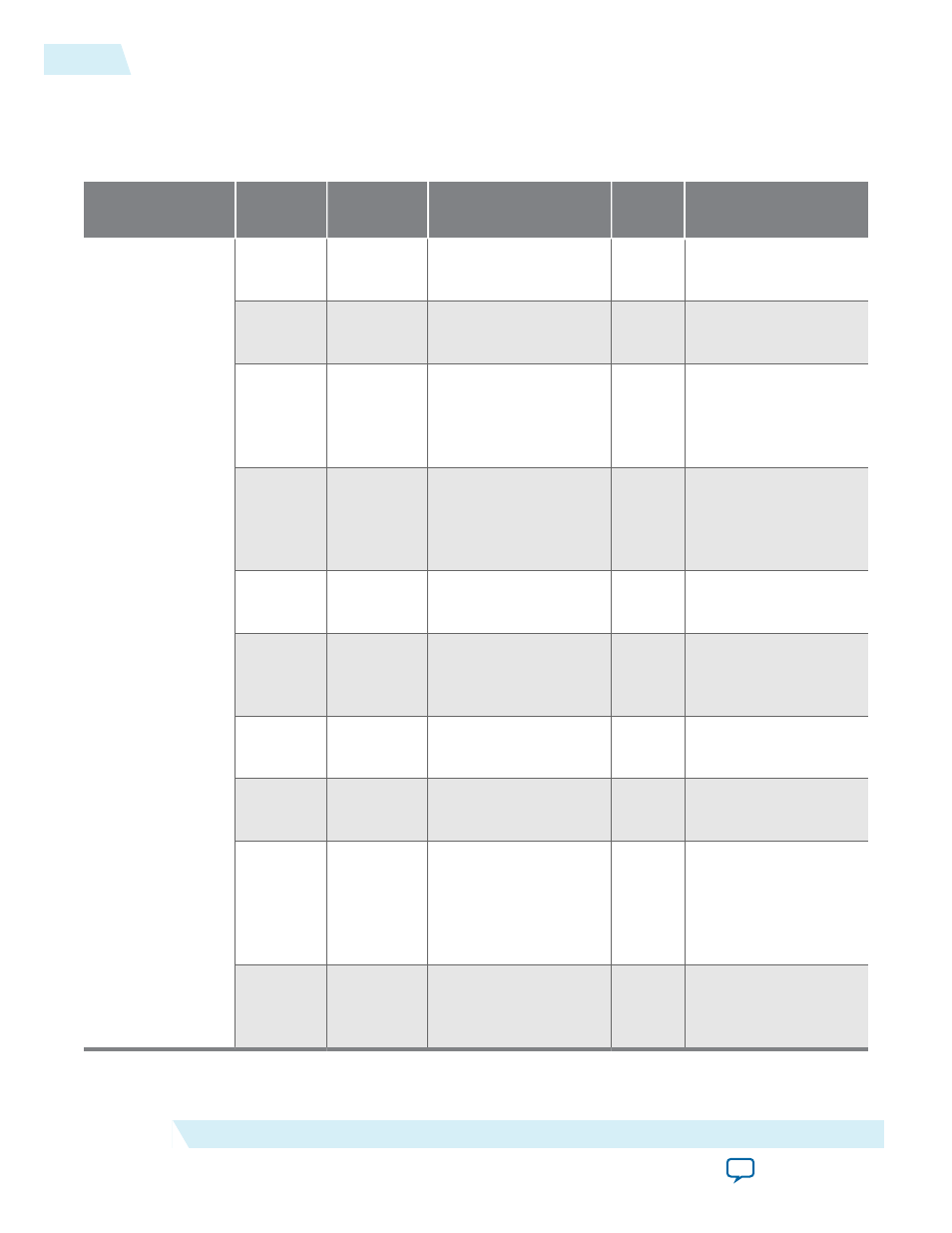

Table 5-9: RX Transceiver Interface

n

is the number of RX lanes,

s

is the number of symbols per clock.

Note: Connect the DisplayPort signals to the Native PHY signals of the same name.

Interface

Port Type

Clock

Domain

Port

Direction

Description

RX transceiver

interface

Clock

N/A

rx_std_clkout[n–1:0]

Input

RX transceiver

recovered clock

Conduit

rx_std_

clkout

rx_parallel_

data[n*s*10–1:0]

Input

Parallel data from RX

transceiver

Conduit

N/A

rx_is_lockedtoref[n–

1:0]

Input

When asserted,

indicates that the RX

CDR PLL is locked to

the reference clock

Conduit

N/A

rx_is_

lockedtodata[n–1:0]

Input

When asserted,

indicates that the RX

CDR PLL is locked to

the incoming data

Conduit

rx_xcvr_

clkout

rx_bitslip[n–1:0]

Output Use to control bit

slipping manually

Conduit

N/A

rx_cal_busy[n–1:0]

Input

Calibration in

progress signal from

RX transceiver

Conduit

xcvr_mgmt_

clk

rx_analogreset[n–

1:0]

Output When asserted, resets

the RX CDR

Conduit

xcvr_mgmt_

clk

rx_digitalreset[n–

1:0]

Output When asserted, resets

the RX PCS

Conduit

xcvr_mgmt_

clk

rx_set_locktoref[n–

1:0]

Output Forces the RX CDR

circuitry to lock to

the phase and

frequency of the

input reference clock

Conduit

xcvr_mgmt_

clk

rx_set_locktodata[n–

1:0]

Output Forces the RX CDR

circuitry to lock to

the received data

5-12

Sink Interfaces

UG-01131

2015.05.04

Altera Corporation

DisplayPort Sink