Clock recovery core parameters, Clock recovery core parameters -5 – Altera DisplayPort MegaCore Function User Manual

Page 66

The clock recovery core produces resynchronized video data together with the following clocks:

• Recovered video pixel clock

• Second clock with twice the recovered pixel clock frequency

The video output data is synchronous to the recovered video clock. You can use the second clock as a

reference clock for the TX transceiver, which is optionally used to serialize the video output data.

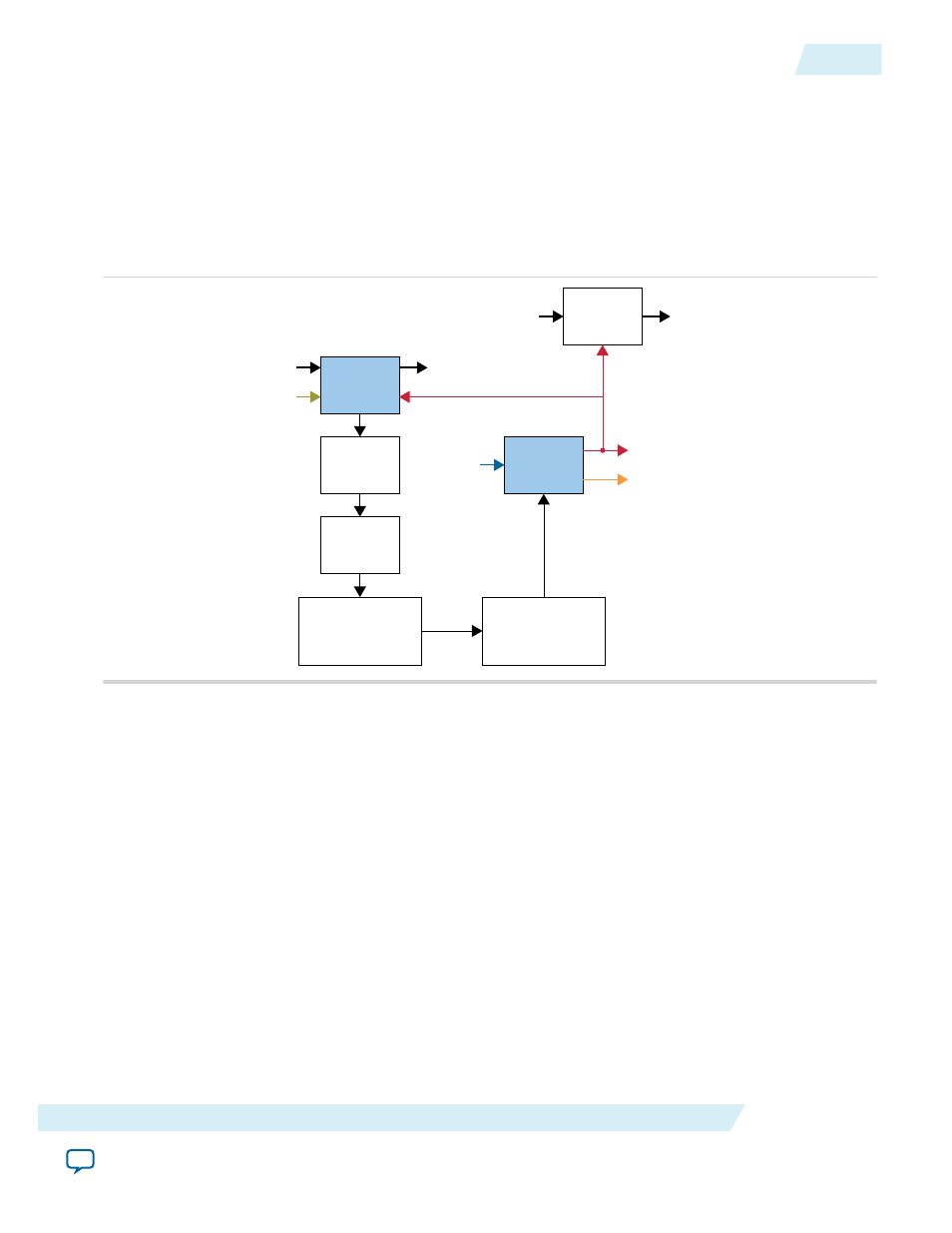

Figure 6-4: Clock Recovery Core Functional Diagram

The following shows a simplified functional diagram of the clock recovery core.

Video Timing

Generator

Altera fPLL

Reconfiguration

Controller

fPLL

Reconfiguration

Avalon Master

fPLL

Controller

Loop

Controller

FIFO

Altera fPLL

RX Link

Clock

Fill Status

RX Video Clock

Video Input Data

Video Output Data

Recovered Video Clock x2

Recovered Video Clock

RX MSA

Video Output Syncs

The clock recovery core clocks the video data input gathered from the DisplayPort sink into a dual-clock

FIFO at the received video clock speed. The core reads from the video data input using the recovered

video clock.

• Video Timing Generator: This block uses the received MSA to create

h-sync

,

v-sync

, and

data

enable

signals that are synchronized to the recovered video clock.

• Loop Controller: This block monitors the FIFO fill level and regulates its throughput by altering the

original Mvid value read from the MSA. The block feeds the modified Mvid to the fPLL Controller,

which calculates a set of parameters suitable for the fPLL Controller. This set of parameters provides

the value to create a recovered video clock frequency corresponding to the new Mvid value. The

calculated fPLL parameters are written by the fPLL Reconfiguration Avalon Master to the Altera fPLL

Reconfiguration Controller internal registers.

• Reconfiguration Controller: This block serializes the parameter values and writes them to the Altera

fPLL IP core.

• Altera fPLL: Generates the recovered video clock and a second clock with twice the frequency.

Clock Recovery Core Parameters

You can use these parameters to configure the clock recovery core.

UG-01131

2015.05.04

Clock Recovery Core Parameters

6-5

DisplayPort IP Core Hardware Demonstration

Altera Corporation