Source clock tree, Source clock tree -19 – Altera DisplayPort MegaCore Function User Manual

Page 35

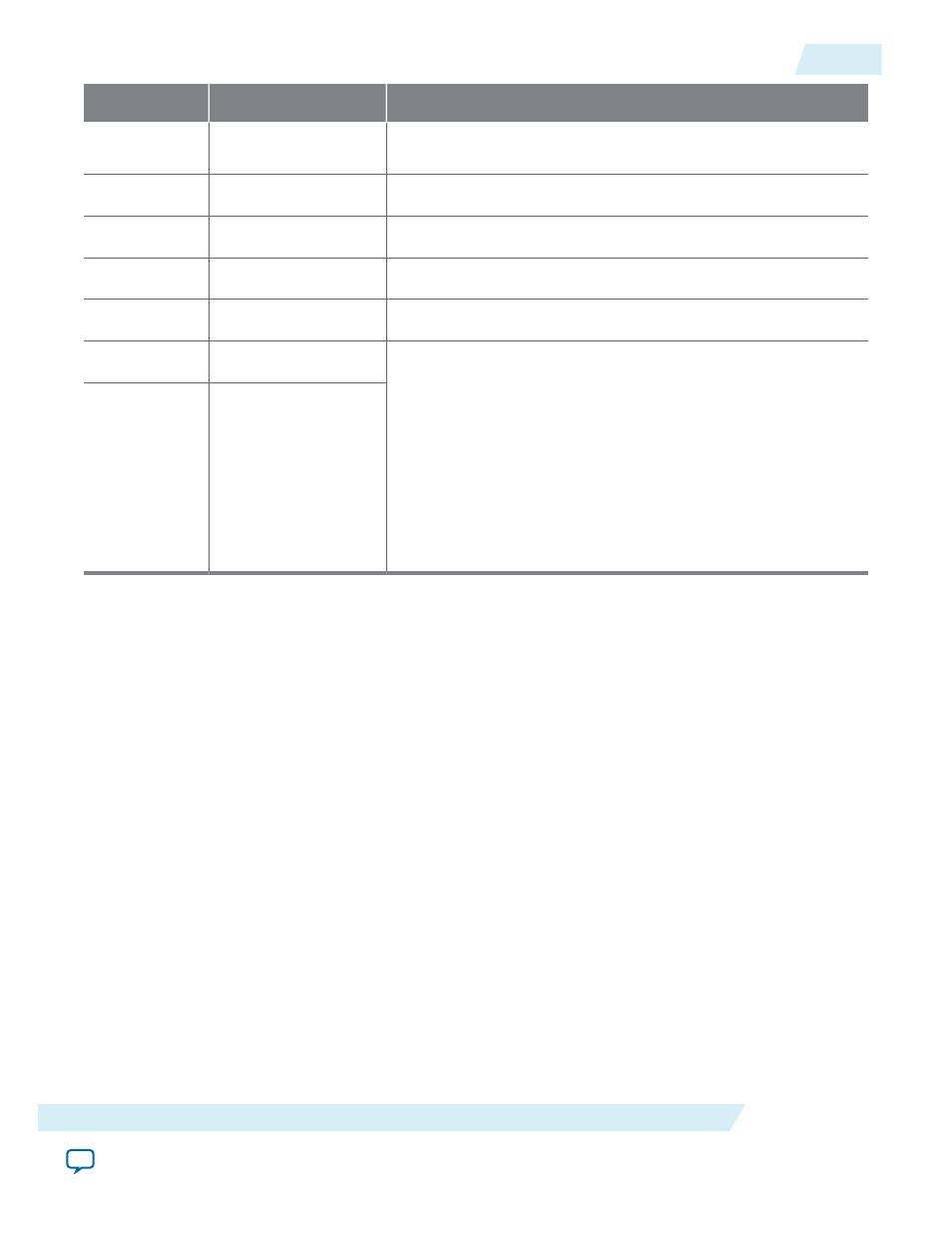

Bit

Signal

Comments

79:64

Vstart[15:0]

Vertical active start from V-sync start in lines (V-sync width +

Vertical back porch)

63

VSP

V-sync polarity 0 = Active high, 1 = Active low

62:48

VSW[14:0]

V-sync width in lines

47:32

Hwidth[15:0]

Active video width in pixels

31:16

Vheight[15:0]

Active video height in lines

15:8

MISC0[7:0]

The

MISC0[7:1]

and

MISC1[7]

fields indicate the color encoding

format. The color depth is indicated in

MISC0[7:5]

:

• 000 - 6 bpc

• 001 - 8 bpc

• 010 - 10 bpc

• 011 - 12 bpc

• 100 - 16 bpc

For details about the encoding format, refer to the DisplayPort

v1.2 specification.

7:0

MISC1[7:0]

Source Clock Tree

The source uses the following clocks:

• Local pixel clock (

txN_vid_clk

), which clocks video data into the IP core.

• Main link clock (

tx_ss_clk

), which clocks data out of the IP core and into the high-speed serial

output (HSSI) components. The main link clock is the output of the CMU PLL clock. You can supply

the CMU PLL with the single reference clock (135 MHz). You can use other frequencies by changing

the CMU PLL divider ratios and/or reconfiguring the transceiver. The 20- or 40- bit data fed to the

HSSI is synchronized to a single HSSI[0] clock. If you select the dual symbol mode option, this clock is

equal to the link rate divided by 20 (270, 135, or 81 MHz). If you turn on quad symbol mode, this clock

is equal to the link rate divided by 40 (135, 67.5, or 40.5 MHz).

• 16 MHz clock (

aux_clk

), which the IP core requires to encode or decode the AUX channel. A separate

clock (

clk

) clocks the Avalon-MM interface.

•

txN_audio_clk

for the audio interface.

UG-01131

2015.05.04

Source Clock Tree

4-19

DisplayPort Source

Altera Corporation