Altera DisplayPort MegaCore Function User Manual

Page 53

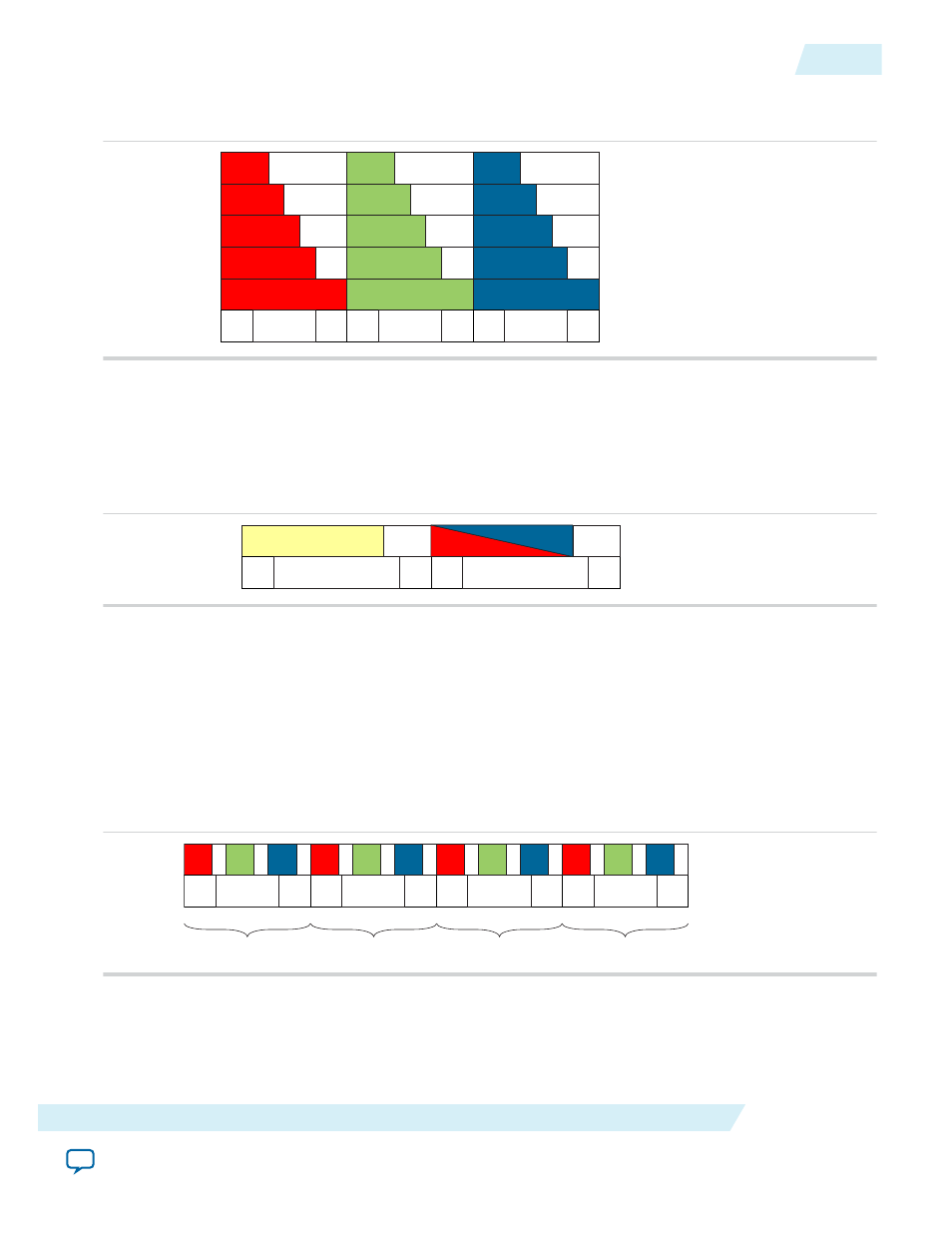

Figure 5-5: Video Output Data Format

18 bpp to 48 bpp Port Width when

rxN_video_out

port width is 48 (16 bpc, 1 Pixel per Clock)

47

32 31

16 15

0 rxN_vid_data[47:0]

18 bpp RGB

24 bpp RGB/YCBCr444 (8 bpc)

30 bpp RGB/YCBCr444 (10 bpc)

36 bpp RGB/YCBCr444 (12 bpc)

48 bpp RGB/YCBCr444 (16 bpc)

The following figure shows the sub-sampled 4:2:2 color format for a video port width of n. The most-

significant half of the video port always transfers the Y component while the least-significant half of the

video port transfers the alternate Cr or Cb component. If the Y/Cb/Cr component widths are less than

n/2, they are most-significant bit aligned with respect to the n and n/2-1 boundaries.

Figure 5-6: Sub-Sampled 4:2:2 Color Format Video Port

n/2-1

0

n - 1

n/2

rxN_vid_data[n - 1:0]

If you set the Pixel output mode option to Dual or Quad, the IP core outputs two or four pixels in

parallel, respectively. To support video resolutions with horizontal active, front and pack porches with

lengths that are not divisible by two or four,

rxN_vid_valid

is widened. For example, for two pixels per

clock,

rxN_vid_valid[0]

is asserted when pixel N belongs to active video and

rxN_vid_valid[1]

is

asserted when pixel n + 1 belongs to active video.

The following figure shows the pixel data order from least significant bits to most significant bits.

Figure 5-7: Video Output Alignment

For RGB 18 bpp when

rxN_video_out

Port Width is 96 (8 bpc, 4 Pixels per Clock)

71

48 47

24 23

0 rxN_vid_data[95:0]

95

72

Pixel 3

Pixel 2

Pixel 1

Pixel 0

Related Information

Provides more information about Clocked Video Input.

UG-01131

2015.05.04

Video Interface

5-17

DisplayPort Sink

Altera Corporation