Dptx_tx_status, Dptx_tx_status -3 – Altera DisplayPort MegaCore Function User Manual

Page 124

Bit

Bit Name

Function

3:0

TP

Current training pattern:

• 0000 = Normal video

• 0001 = Training pattern 1

• 0010 = Training pattern 2

• 0011 = Training pattern 3

• 0111 = Video idle pattern

• 1001 = D10.2 test pattern (same as training pattern 1)

• 1010 = Symbol error rate measurement pattern

• 1011 = PRBS7

• 1100 = 80-bit custom pattern

• 1101 = HBR2 compliance test pattern (CP2520 pattern 1)

DPTX_TX_STATUS

The IP core issues an IRQ to the Nios II processor if the

DPTX_TX_CONTROL

registers

HPD_IRQ_EN

is 1 and

the IP core detects a new HPD event.

HPD_EVENT

provides information about the event that caused the

interrupt. The interrupt and

HPD_EVENT

bit fields are both cleared by reading the

DPTX_TX_STATUS

register.

Address: 0×0001

Direction: CRO

Reset: 0×00000000

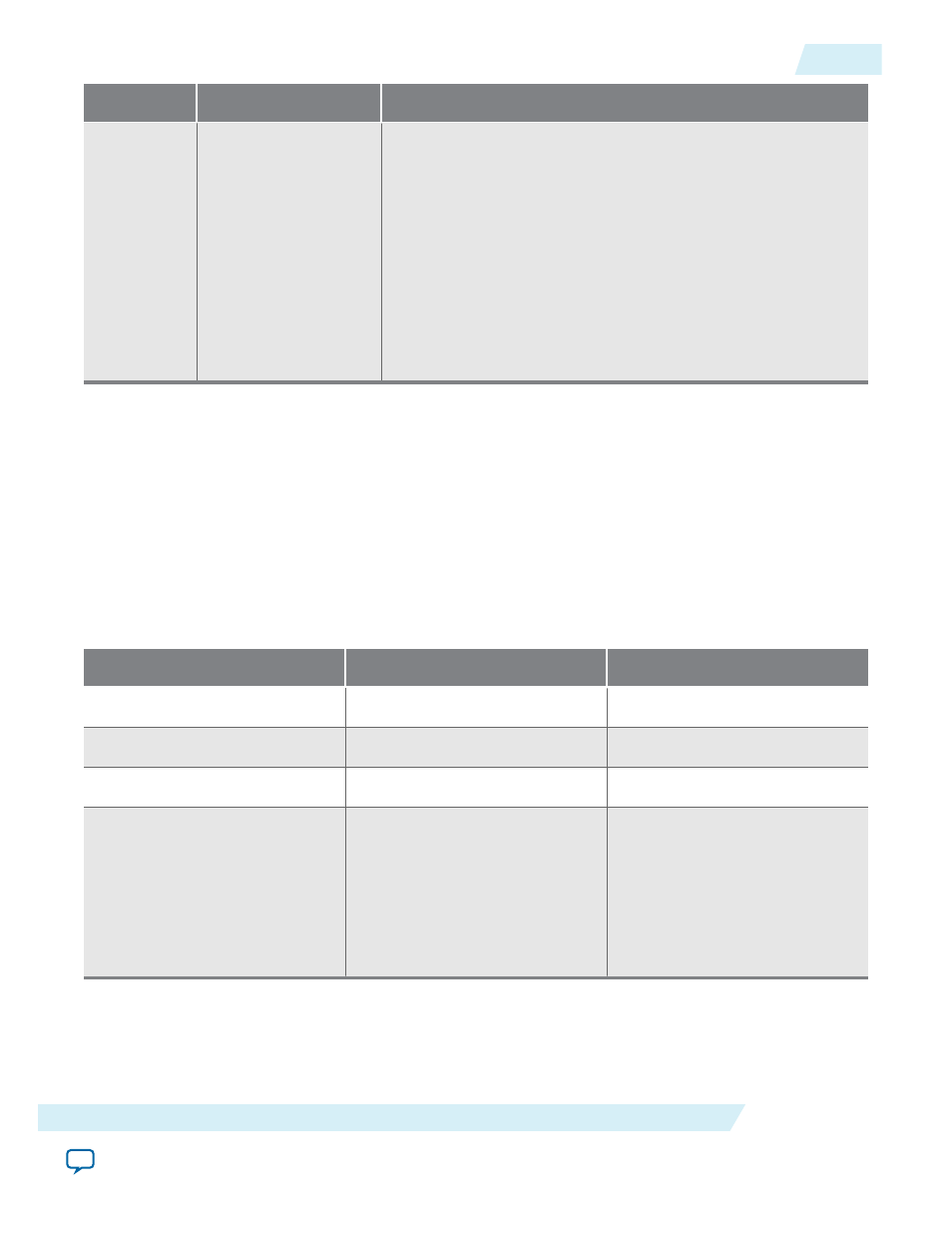

Table 9-3: DPTX_TX_STATUS Bits

Bit

Bit Name

Function

31:4

Unused

3

RESERVED

Reserved

2

HPD_LEVEL

Current HPD logic level

1:0

HPD_EVENT

HPD event causing IRQ (read to

clear):

• 00 = No event

• 01 = HPD plug event (long

HPD)

• 10 = HPD IRQ (short HPD)

• 11 = Reserved

UG-01131

2015.05.04

DPTX_TX_STATUS

9-3

DisplayPort Source Register Map and DPCD Locations

Altera Corporation