Device family support, Ip core verification, Performance and resource utilization – Altera DisplayPort MegaCore Function User Manual

Page 12: Device family support -2, Ip core verification -2, Performance and resource utilization -2

Device Family Support

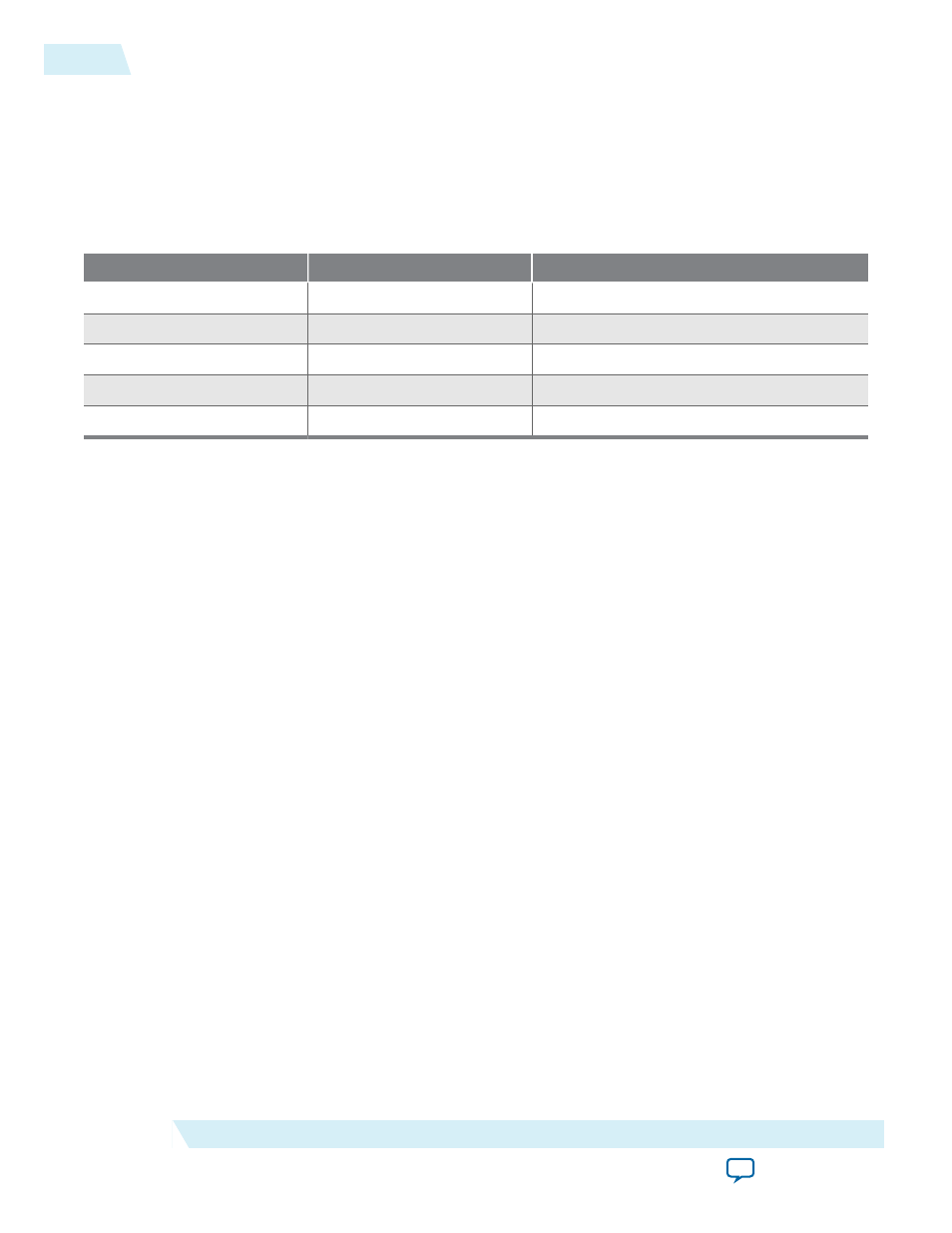

The following table lists the link rate support offered by the DisplayPort IP core for each Altera device

family.

Table 2-1: Link Rate Support by Device Family

RBR = Reduced Bit Rate, HBR = High Bit Rate

Device Family

20-bit mode

40-bit mode

Arria 10

RBR, HBR, HBR2

RBR, HBR, HBR2

Arria V GX

RBR, HBR

RBR, HBR, HBR2

Arria V GZ

RBR, HBR, HBR2

RBR, HBR, HBR2

Cyclone V

RBR, HBR

RBR, HBR

Stratix V

RBR, HBR, HBR2

RBR, HBR, HBR2

IP Core Verification

Before releasing a publicly available version of the DisplayPort IP core, Altera runs a comprehensive

verification suite in the current version of the Quartus

®

II software. These tests use standalone methods

and the Qsys system integration tool to create the instance files. These files are tested in simulation and

hardware to confirm functionality. Altera tests and verifies the DisplayPort IP core in hardware for

different platforms and environments.

The DisplayPort IP core has been tested at VESA Plugtest events and passes the Unigraf DisplayPort Link

Layer CTS tests.

Performance and Resource Utilization

This section contains tables showing IP core variation size and performance examples.

The following table lists the resources and expected performance for selected variations. The results were

obtained using the Quartus II software v15.0 for the following devices:

• Arria V (5AGXFB3H4F40C5)

• Cyclone V (5CGTFD9E5F35C7)

• Stratix V (5SGXEA7K2F40C2)

• Arria 10 (10AX115S2F45I2SGES)

2-2

Device Family Support

UG-01131

2015.05.04

Altera Corporation

About This IP Core