Transceiver and clocking, Transceiver and clocking -11 – Altera DisplayPort MegaCore Function User Manual

Page 72

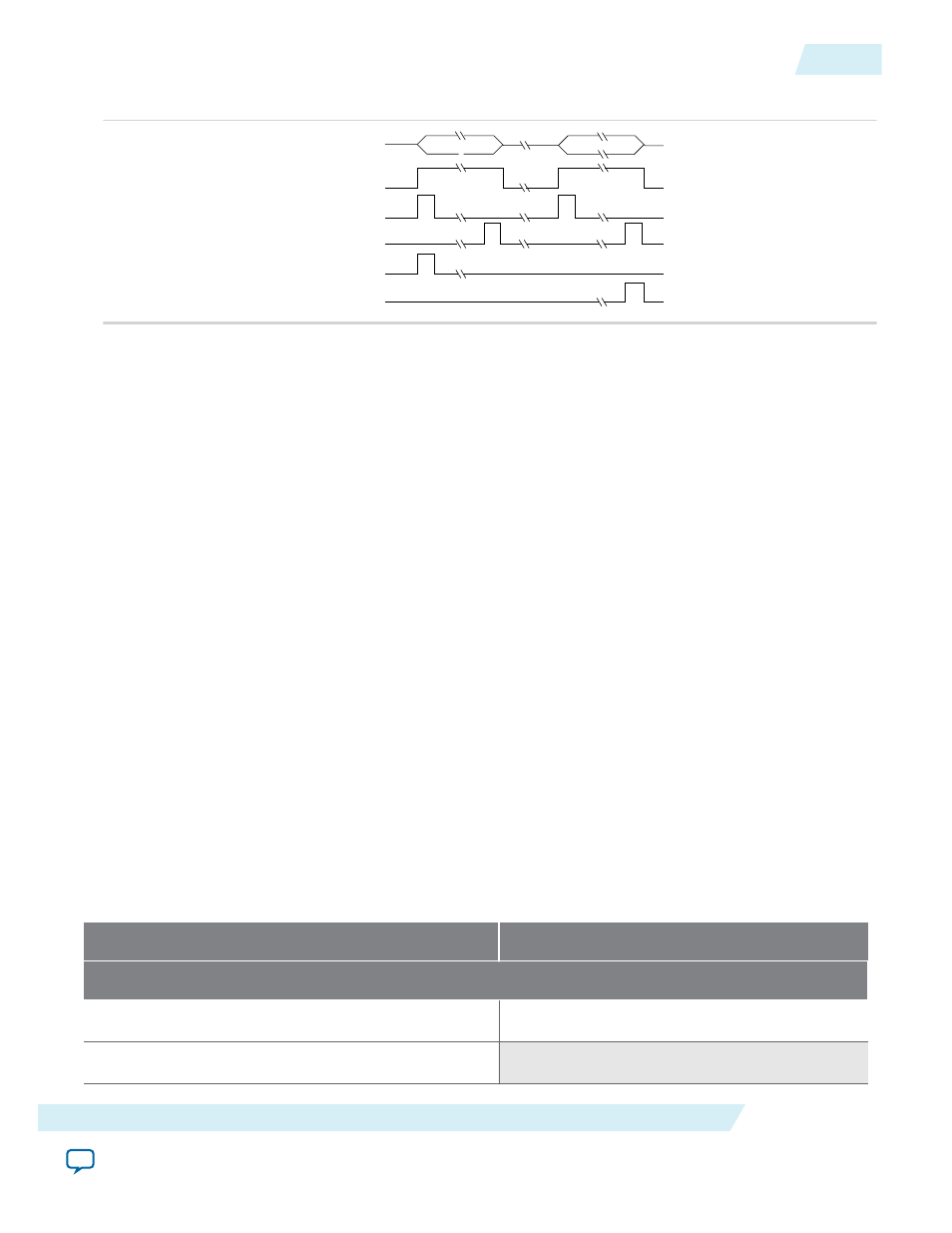

Figure 6-5: Video Input Port Timing Diagram

vidin_data

vidin_valid

vidin_sol

vidin_eol

vidin_sof

vidin_oef

When the PIXELS_PER_CLOCK parameter is greater than 1, all input pixels are supposed to be valid

when you assert

vidin_valid

. The parameter only supports timings with horizontal active width divisible

by 2 (PIXELS_PER_CLOCK = 2) or 4 (PIXELS_PER_CLOCK = 4).

The clock recovery core video output port produces pixel data with standard

hsync

,

vsync

, or

de

timing.

All signals are synchronous to the reconstructed video clock

rec_clk

, unless mentioned otherwise. For

designs using a TX transceiver, you can use

rec_clk

as its reference clock.

You can use

rec_clk_x2

as a reference clock for transceivers that have reference clocks with frequencies

lower than the minimum pixel clock frequency received. For example, the Video Graphics Array (VGA)

25-MHz resolution when the transceiver's minimum reference clock is 40 MHz.

The clock recovery core asserts

reset_out

when the remaining port signals are not valid. For example,

during a recovered video resolution change when the

rec_clk

and

rec_clk_x2

signals are not yet locked

and stable. Altera recommends that you use

reset_out

to reset the downstream logic connected to the

video output port.

During the hardware demonstration operation, you can adjust the DisplayPort source resolution

(graphics card) from the PC and observe the effect on the IP core. The Nios II software prints the source

and sink AUX channel activity. Press one of the push buttons to print the current TX and RX MSA.

Transceiver and Clocking

The device’s Gigabit transceivers operate at 5.4, 2.7, and 1.62 Gbps and require a 135-MHz single

reference clock. When the link rate changes, the state machine only reconfigures the transceiver PLL

settings.

Table 6-4: Arria V Transceiver Native PHY TX and RX Settings

The table shows the Arria V Transceiver Native PHY settings for TX and RX using a single reference clock.

Parameters

Single Reference Clock Settings

Datapath Options

Enable TX datapath

On

Enable RX datapath

On

UG-01131

2015.05.04

Transceiver and Clocking

6-11

DisplayPort IP Core Hardware Demonstration

Altera Corporation