Embedded displayport (edp) support, Source parameters, Embedded displayport (edp) support -5 – Altera DisplayPort MegaCore Function User Manual

Page 21: Source parameters -5

Embedded DisplayPort (eDP) Support

The DisplayPort IP core is compliant with eDP version 1.3. eDP is based on the VESA DisplayPort

standard. It has the same electrical interface and can share the same video port on the controller. The

DisplayPort IP core supports:

• Full (normal) link training—default

• Fast link training—mandatory eDP feature

Source Parameters

You set parameters for the source using the DisplayPort parameter editor.

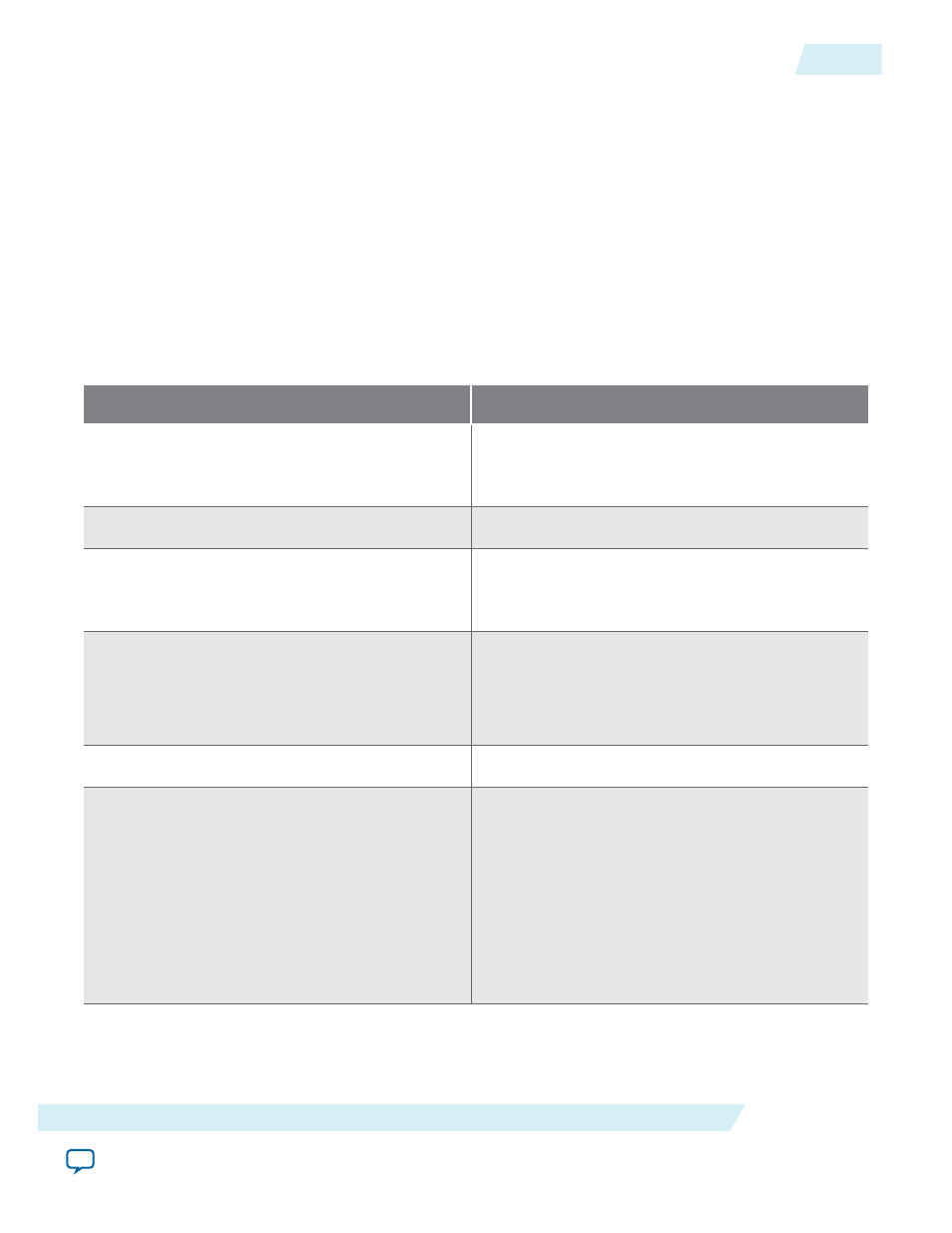

Table 4-1: Source Parameters

Parameter

Description

Device family

Select the targeted device family—Arria 10, Arria V

GX, Arria V GZ, Cyclone V, or Stratix V—matches

the project device family.

Support DisplayPort source

Turn on to enable DisplayPort source.

Maximum video input color depth

Select the video input interface port bits per color.

Determines top-level video input port width (for

example, 6 bpc = 18 bpp, 16 bpc = 48 bpp).

TX maximum link rate

Select the the maximum link rate. 5.4 Gbps, 2.7

Gbps, 1.62 Gbps.

Note: Cyclone V devices do not support 5.4

Gbps.

Maximum lane count

Select the maximum lanes desired (1, 2, or 4).

Symbol output mode

Specify how many symbols are transferred during

each clock cycle: dual or quad symbol, or TX

transceiver data width: dual (20 bits) or quad (40

bits).

Dual symbol mode saves logic resource but requires

the core to run at twice the clock frequency of quad

symbol mode. If timing closure is a problem in the

device, you should consider using quad symbol

mode.

UG-01131

2015.05.04

Embedded DisplayPort (eDP) Support

4-5

DisplayPort Source

Altera Corporation