Altera DisplayPort MegaCore Function User Manual

Page 13

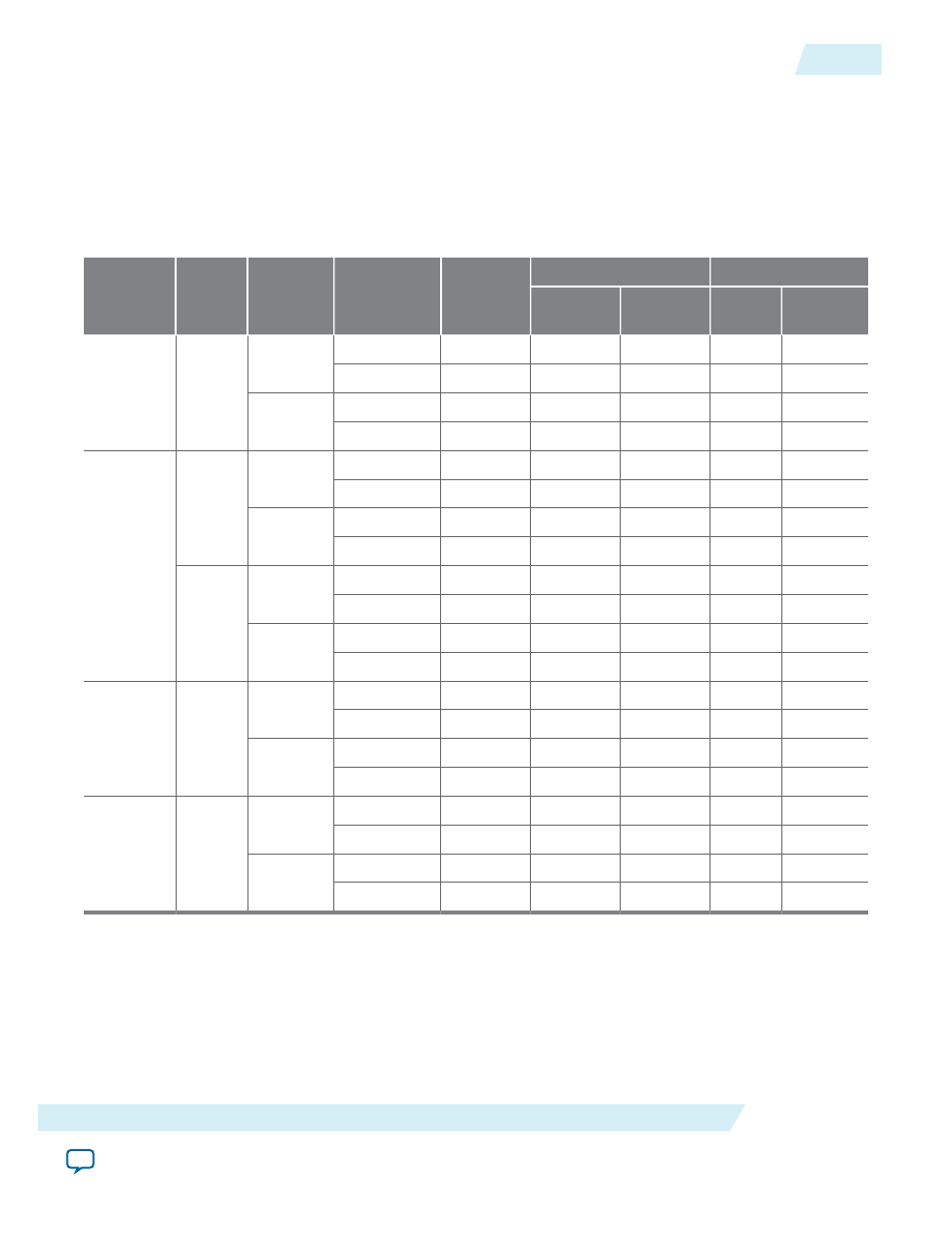

Table 2-2: DisplayPort IP Core FPGA Resource Utilization

The table below shows the resource information for Arria V and Cyclone V devices using M10K; Arria 10 and

Stratix V devices using M20K. The resources were obtained using the following parameter settings:

• Mode = duplex

• Maximum lane count = 4 lanes

• Maximum video input color depth = 24 bits per pixel (bpp)

• Pixel input mode = 1 pixel per clock

Device

Streams

Direction

Symbol per

Clock

ALMs

Logic Registers

Memory

Primary

Secondary

Bits

M10K or

M20K

Arria 10

Single

stream

(SST)

RX

Dual

7,087

9,580

1,001

16,576

30

Quad

9,957

11,121

1,153

31,424

30

TX

Dual

16,075

10,205

465

27,424

27

Quad

29,075

13,605

646

39,776

40

Arria V

GX

SST

RX

Dual

7,176

9,432

1,015

16,576

30

Quad

9,881

10,793

1,221

31,424

30

TX

Dual

16,340

10,213

499

27,424

27

Quad

29,258

13,568

715

39,776

40

MST

(2

streams)

RX

Dual

13,337

15,901

1,650

30,336

52

Quad

20,913

19,551

1,952

57,472

52

TX

Dual

31,790

20,095

879

47,680

54

Quad

58,333

27,433

1,357

65,472

80

Cyclone

V GX

SST

RX

Dual

7,137

9,446

1,035

16,576

30

Quad

9,817

10,886

1,229

31,424

30

TX

Dual

16,343

10,157

604

27,424

27

Quad

29,326

13,537

825

39,776

40

Stratix

V GX

SST

RX

Dual

7,006

9,569

966

15,552

28

Quad

9,967

11,087

1,065

30,400

28

TX

Dual

16,340

10,213

499

27,424

27

Quad

29,258

13,568

715

39,776

40

Related Information

More information about Quartus II resource utilization reporting.

UG-01131

2015.05.04

Performance and Resource Utilization

2-3

About This IP Core

Altera Corporation