Avalon-st input interface, Command generator, Timing bank pool – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 96

6–2

Chapter 6: Functional Description—High-Performance Controller II

Memory Controller Architecture

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Figure 6–2

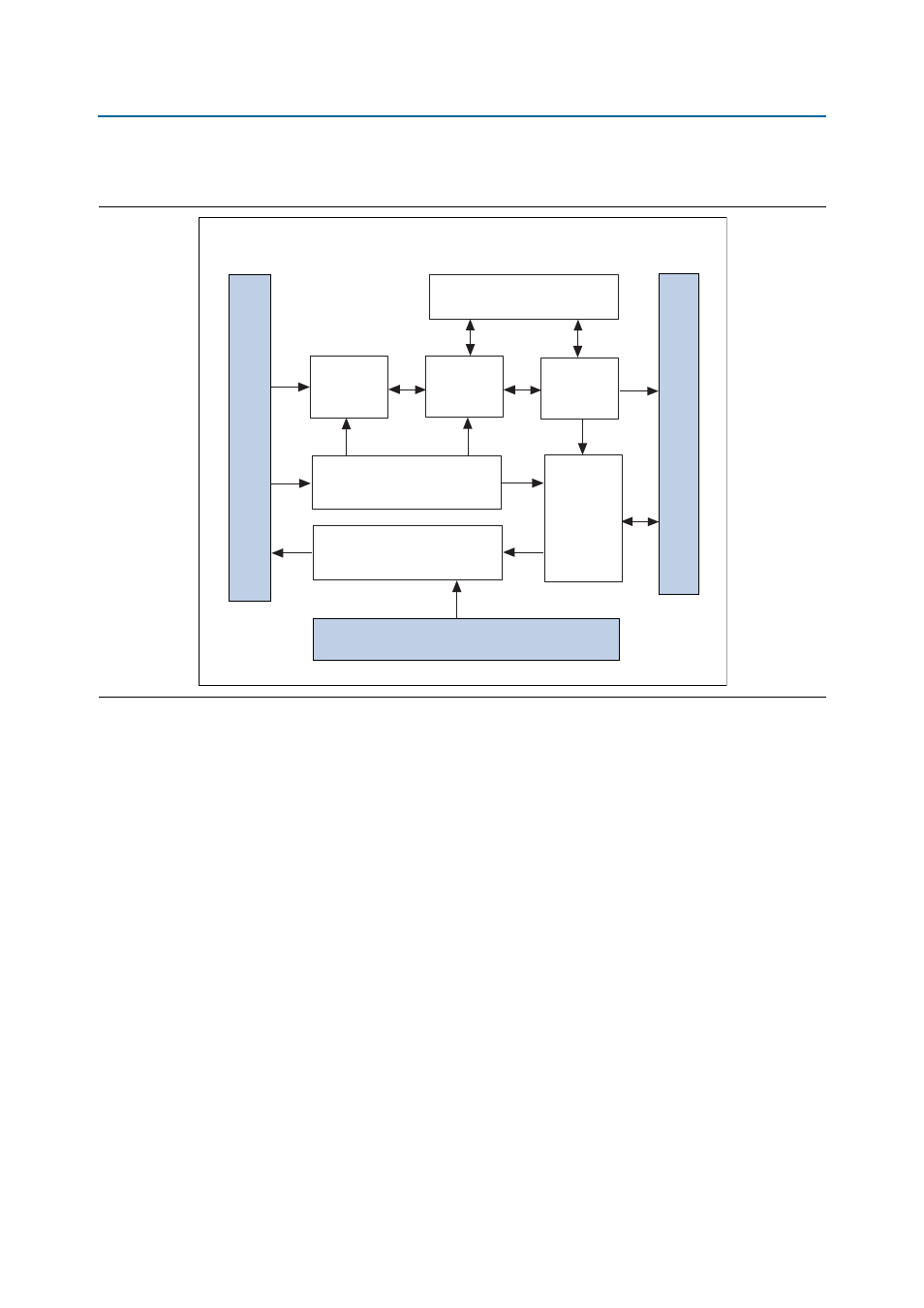

shows a block diagram of the memory controller architecture.

The following sections describe the blocks in

Figure 6–2

.

Avalon-ST Input Interface

The Avalon-ST interface serves as the entry point to the memory controller, and

provides communication with the requesting data masters.

f

For information about the Avalon interface, refer to

Command Generator

The command generator accepts commands from the front-end Avalon-ST interface

and from local ECC internal logic, and provides those commands to the timing bank

pool.

Timing Bank Pool

The timing bank pool is a parallel queue that works with the arbiter to enable data

reordering. The timing bank pool tracks incoming requests, ensures that all timing

requirements are met and, upon receiving write-data-ready notification from the

write data buffer, passes the requests to the arbiter in an ordered and efficient manner.

Figure 6–2. Memory Controller Architecture Block Diagram

CSR Interface

Avalon-ST Input Interface

AFI Interface to PHY

Rank Timer

Write Data Buffer

Read Data Buffer

Command

Generator

Timing Bank

Pool

Arbiter

ECC

Memory Controller