Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 120

6–26

Chapter 6: Functional Description—High-Performance Controller II

Register Maps

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

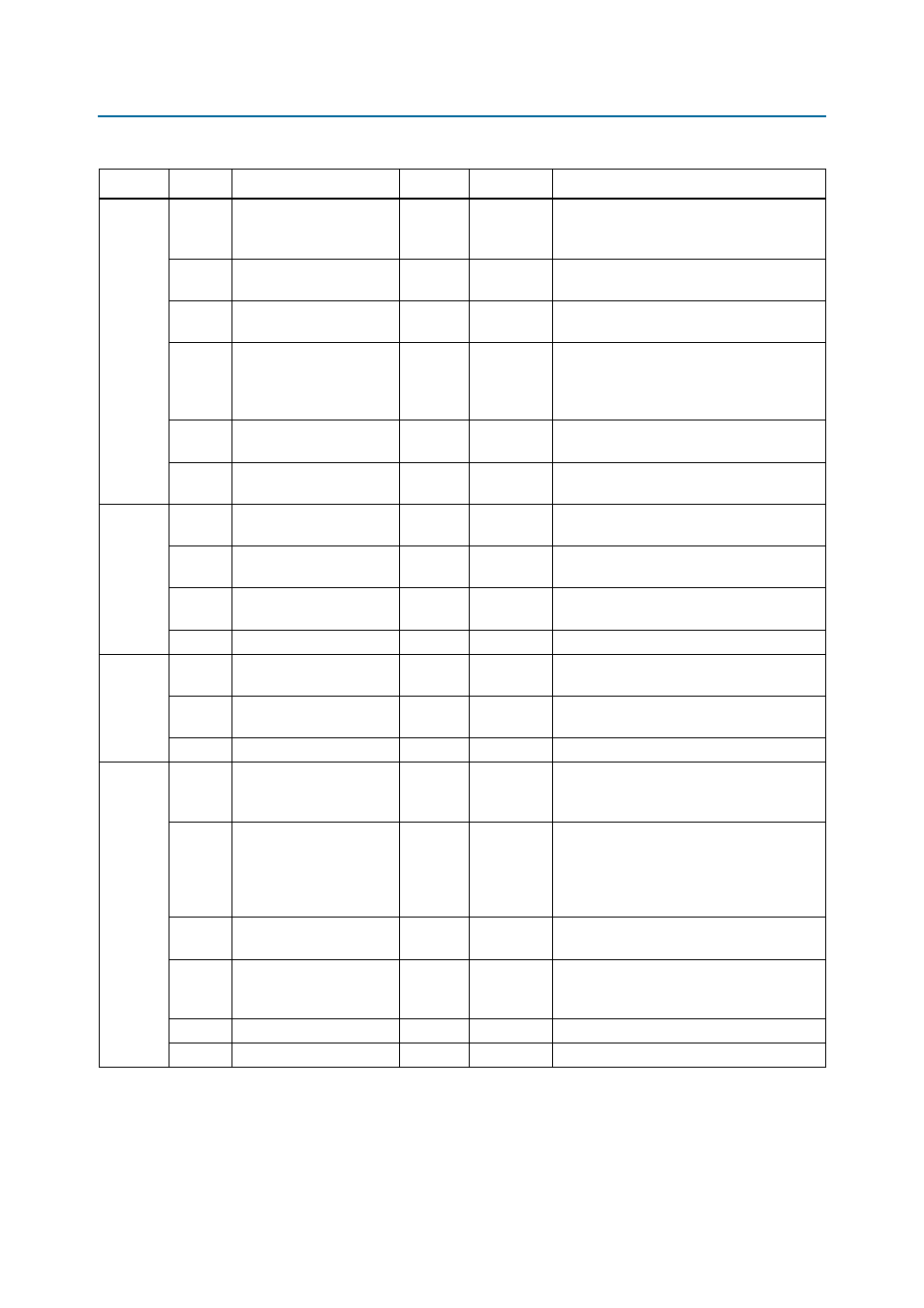

0x123

3:0

t

RCD

—

Read write

The activate to read or write a timing

parameter. The range of legal values is 2-11

cycles.

7:4

t

RRD

—

Read write

The activate to activate a timing parameter.

The range of legal values is 2-8 cycles.

11:8

t

RP

—

Read write

The precharge to activate a timing parameter.

The range of legal values is 2-11 cycles.

15:12

t

MRD

—

Read write

The mode register load time parameter. This

value is not used by the controller, as the

controller derives the correct value from the

memory type setting.

23:16

t

RAS

—

Read write

The activate to precharge a timing parameter.

The range of legal values is 4-29 cycles.

31:24

t

RC

—

Read write

The activate to activate a timing parameter.

The range of legal values is 8-40 cycles.

0x124

3:0

t

WTR

—

Read write

The write to read a timing parameter. The

range of legal values is 1-10 cycles.

7:4

t

RTP

—

Read write

The read to precharge a timing parameter.

The range of legal values is 2-8 cycles.

15:8

t

FAW

—

Read write

The four-activate window timing parameter.

The range of legal values is 6-32 cycles.

31:16

Reserved.

0

—

Reserved for future use.

0x125

15:0

t

REFI

—

Read write

The refresh interval timing parameter. The

range of legal values is 780-6240 cycles.

23:16

t

RFC

—

Read write

The refresh cycle timing parameter. The

range of legal values is 12-88 cycles.

31:24

Reserved.

0

—

Reserved for future use.

0x126

3:0

CAS latency, t

CL

—

Read write

This value must be set to match the memory

CAS latency. You must set this value in the

0x04 register map as well.

7:4

Additive latency, AL

Additive latency setting. The default value for

these bits is set in the Memory additive CAS

latency setting in the Preset Editor dialog

box. You must set this value in the 0x05

register map as well.

11:8

CAS write latency, CWL

CAS write latency setting. You must set this

value in the 0x06 register map as well.

15:12

Write recovery, t

WR

This value must be set to match the memory

write recovery time (t

WR

). You must set this

value in the 0x04 register map as well.

19:16

Burst Length

—

Read write

Value must match memory burst length.

31:20

Reserved.

0

—

Reserved for future use.

Table 6–15. Controller Register Map (Part 3 of 5)

Address

Bit

Name

Default

Access

Description