Generation of ctl_rdata_valid, Cas write latency, Additive latency – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 91: Datapath latencies and relative phases, Board layout

Chapter 5: Functional Description—ALTMEMPHY

5–45

Using a Custom Controller

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

■

Generation of ctl_rdata_valid

■

Dynamic termination (Rt) control timing

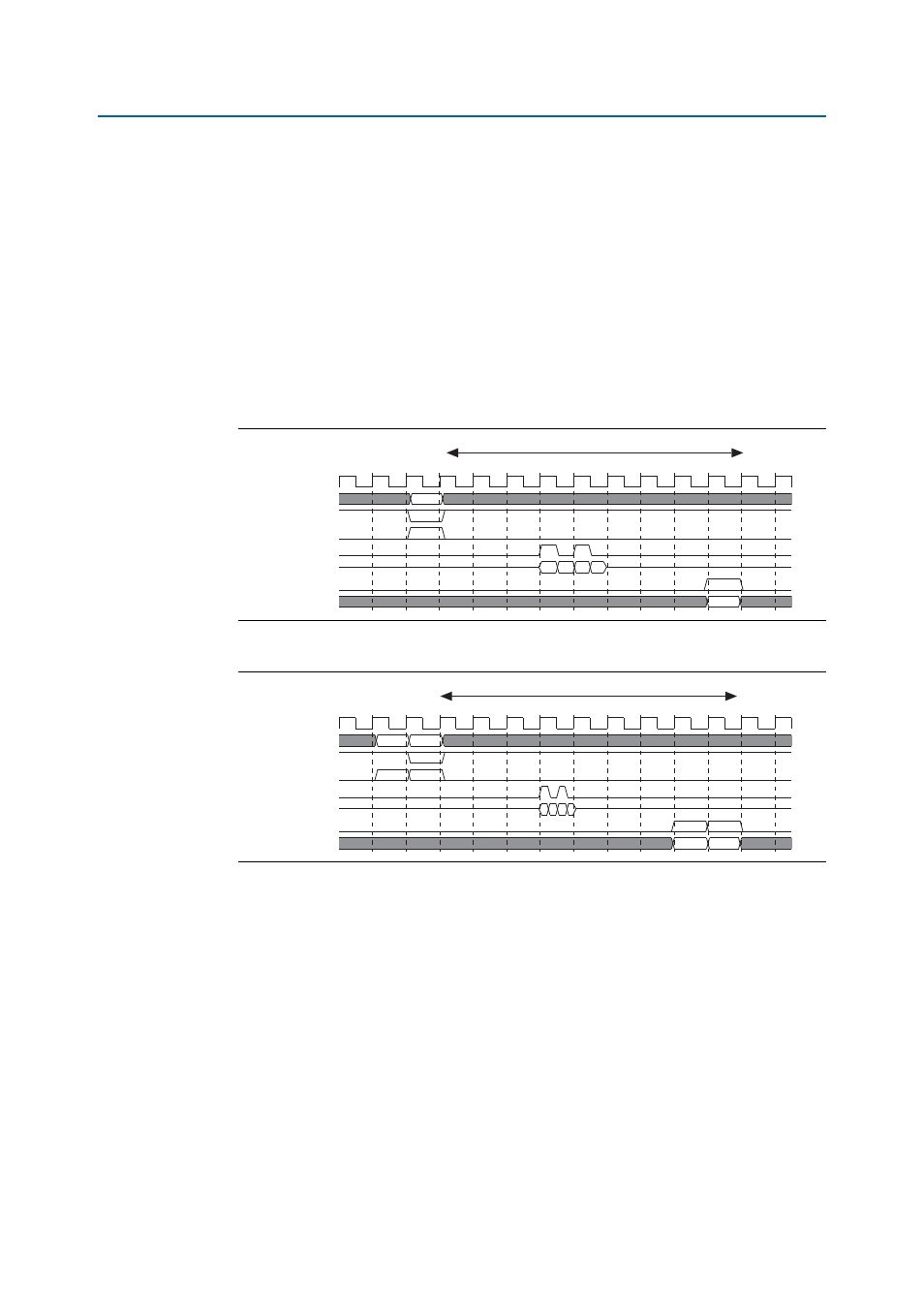

The read latency, ctl_rlat, is advertised back to the controller. This signal indicates

how long it takes in ctl_clk clock cycles from assertion of the ctl_doing_read signal

to valid read data returning on ctl_rdata. The ctl_rlat signal is only valid when

calibration has successfully completed and never changes values during normal user

mode operation.

The ALTMEMPHY provides a signal, ctl_rdata_valid, to indicate that the data on

read data bus is valid. The width of this signal varies between half-rate and full-rate

designs to support the option to indicate that the read data is not word aligned.

Figure 5–21

and

Figure 5–22

show these relationships.

Handshake Mechanism Between Write Commands and Write Data

In the AFI, the ALTMEMPHY output ctl_wlat gives the number of ctl_clk cycles

between the write command that is issued ctl_cs_n asserted and ctl_dqs_burst

asserted. The ctl_wlat signal takes account of the following actions to provide a

single value in ctl_clk clock cycles:

■

CAS write latency

■

Additive latency

■

Datapath latencies and relative phases

■

Board layout

■

Address and command path latency and 1T register setting, which is dynamically

setup to take into account any leveling effects

Figure 5–21. Address and Command and Read-Path Timing—Full-Rate Design

Figure 5–22. Second Read Alignment—Half-Rate Design

ctl_clk

ctl_addr

ctl_cs_n

ctl_doing_read

mem_dqs

mem_dq

ctl_rdata_valid

ctl_rdata

ctl_rlat = 9

1 2 3 4 5 6 7 8 9

ctl_clk

1 2 3 4 5 6 7 8 9

ctl_rlat = 9

ctl_addr

ctl_cs_n

ctl_doing_read

mem_dqs

mem_dq

ctl_rdata_valid

ctl_rdata

A

XA

10

10

10

01

01

10

01

01

DX

XD