Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 117

Chapter 6: Functional Description—High-Performance Controller II

6–23

Register Maps

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

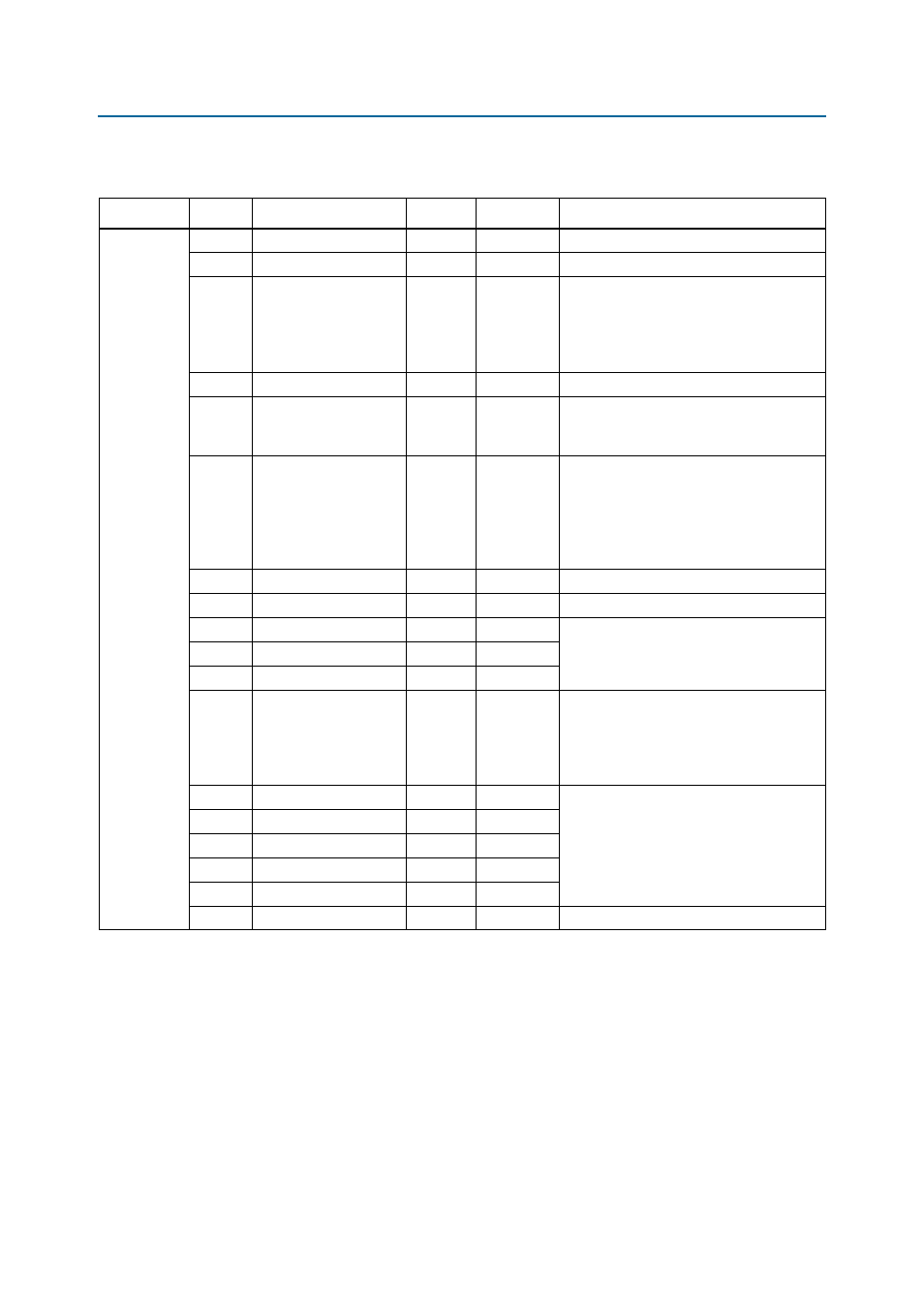

Table 6–14. ALTMEMPHY Register Map (Part 1 of 2)

Address

Bit

Name

Default

Access

Description

0x005

2:0

Burst length

8

Read only

This value is set to 8.

3

BT

0

Read only

This value is set to 0.

6:4

CAS latency

—

Read write

CAS latency setting. The default value for

these bits is set by the MegaWizard CAS

Latency setting for your controller instance.

You must set this value in the CSR interface

register map 0x126 as well.

7

Reserved

0

—

Reserved for future use.

8

DLL

0

Read write

Not used by the controller, but you can set

and program into the memory device mode

register.

11:9

Write recovery

—

Read write

Write recovery (t

WR

) setting. The default

value for these bits is set by the

MegaWizard Write Recovery setting for

your controller instance. You must set thi

svalue in CSR interface register map 0x126

as well.

12

PD

0/1

Read only

This value is set to 0.

15:13

Reserved

0

C

Reserved for future use.

16

DLL

0

Read write

Not used by the controller, but you can set

and program into the memory device mode

register.

17

ODS

0

Read write

18

RTT

0

Read write

21:19

AL

—

Read write

Additive latency setting. The default value

for these bits is set by the MegaWizard

Additive Latency setting for your controller

instance. You must set this value in CSR

interface register map 0x126 as well.

22

RTT

0

Read write

Not used by the controller, but you can set

and program into the memory device mode

register.

25:23

RTT/WL/OCD

0

Read write

26

DQS#

0

Read write

27

TDQS/RDQS

0

Read write

28

QOFF

0

Read write

31:29

Reserved

0

—

Reserved for future use.