Phy-to-controller interfaces, Phy-to-controller interfaces –34 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 80

5–34

Chapter 5: Functional Description—ALTMEMPHY

PHY-to-Controller Interfaces

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

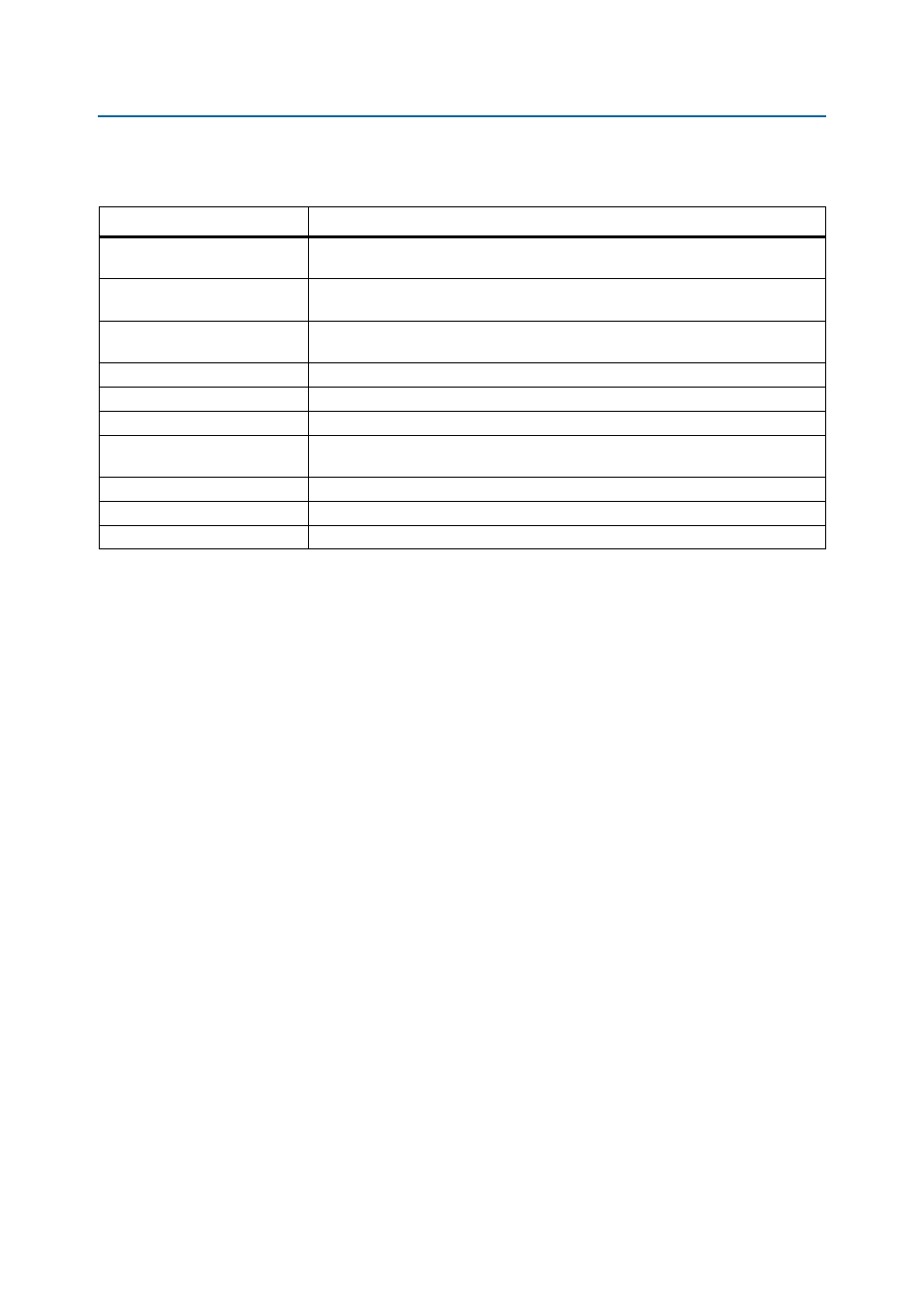

Table 5–8

shows the parameters that

Table 5–5

through

Table 5–7

refer to.

PHY-to-Controller Interfaces

The following section describes the typical modules that are connected to the

ALTMEMPHY variation and the port name prefixes each module uses. This section

also describes using a custom controller. This section describes the AFI.

The AFI standardizes and simplifies the interface between controller and PHY for all

Altera memory designs, thus allowing you to easily interchange your own controller

code with Altera's high-performance controllers. The AFI includes an administration

block that configures the memory for calibration and performs necessary mode

registers accesses to configure the memory as required (these calibration processes are

different).

Figure 5–11

shows an overview of the connections between the PHY, the

controller, and the memory device.

Table 5–8. Parameters

Parameter Name

Description

DWIDTH_RATIO

The data width ratio from the local interface to the memory interface. DWIDTH_RATIO of

2 means full rate, while DWIDTH_RATIO of 4 means half rate.

LOCAL_IF_DWIDTH

The width of the local data bus must be quadrupled for half-rate and doubled for

full-rate.

MEM_IF_DWIDTH

The data width at the memory interface. MEM_IF_DWIDTH can have values that are

multiples of MEM_IF_DQ_PER_DQS.

MEM_IF_DQS_WIDTH

The number of DQS pins in the interface.

MEM_IF_ROWADDR_WIDTH

The row address width of the memory device.

MEM_IF_BANKADDR_WIDTH

The bank address with the memory device.

MEM_IF_CS_WIDTH

The number of chip select pins in the interface. The sequencer only calibrates one chip

select pin.

MEM_IF_DM_WIDTH

The number of mem_dm pins on the memory interface.

MEM_IF_DQ_PER_DQS

The number of mem_dq[] pins per mem_dqs pin.

MEM_IF_CLK_PAIR_COUNT

The number of mem_clk/mem_clk_n pairs in the interface.