Resource utilization, Resource utilization –5 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 11

Chapter 1: About This IP

1–5

Resource Utilization

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Resource Utilization

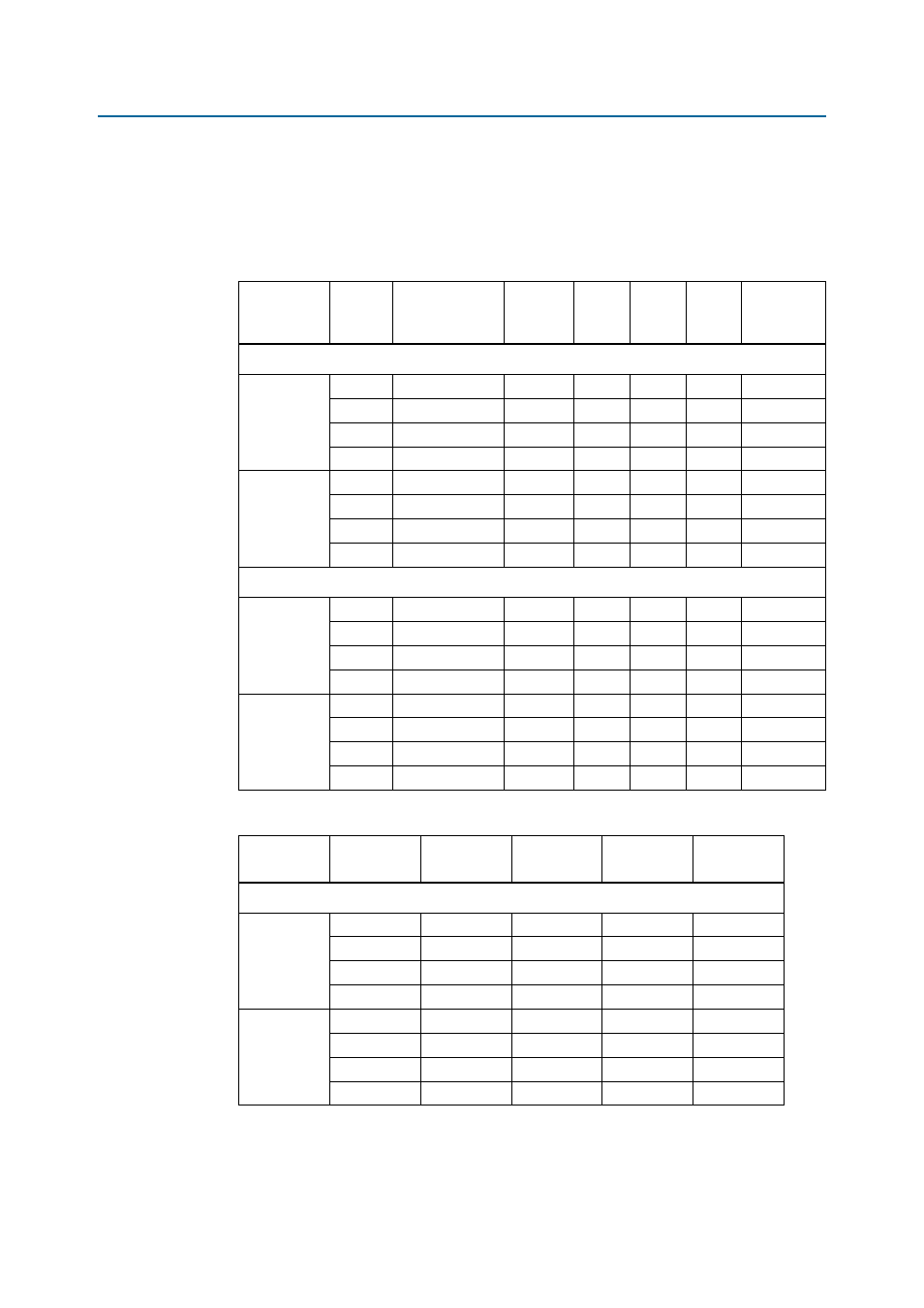

show typical resource utilization data for the DDR2

high-performance controller and controller plus PHY, for half-rate and full-rate

configurations.

Table 1–4. DDR2 Resource Utilization in Arria II GX Devices

Protocol

Memory

Width

(Bits)

Combinational

ALUTS

Logic

Registers

Mem

ALUTs

M9K

Blocks

M144K

Blocks

Memory

(Bits)

Controller

DDR2

(Half rate)

8

1,971

1,547

10

2

0

4,352

16

1,973

1,547

10

4

0

8,704

64

2,028

1,563

18

15

0

34,560

72

2,044

1,547

10

17

0

39,168

DDR2

(Full rate)

8

2,007

1,565

10

2

0

2,176

16

2,013

1,565

10

2

0

4,352

64

2,022

1,565

10

8

0

17,408

72

2,025

1,565

10

9

0

19,584

Controller+PHY

DDR2

(Half rate)

8

3,481

2,722

12

4

0

4,672

16

3,545

2,862

12

7

0

9,280

64

3,891

3,704

20

24

0

36,672

72

3,984

3,827

12

26

0

41,536

DDR2

(Full rate)

8

3,337

2,568

29

2

0

2,176

16

3,356

2,558

11

4

0

4,928

64

3,423

2,836

31

12

0

19,200

72

3,445

2,827

11

14

0

21,952

Table 1–5. DDR2 Resource Utilization in Cyclone III Devices (Part 1 of 2)

Protocol

Memory

Width (Bits)

Logic

Registers

Logic Cells

M9K Blocks

Memory

(Bits)

Controller

DDR2

(Half rate)

8

1,513

3,015

4

4,464

16

1,513

3,034

6

8,816

64

1,513

3,082

18

34,928

72

1,513

3,076

19

39,280

DDR2

(Full rate)

8

1,531

3,059

4

2,288

16

1,531

3,108

4

4,464

64

1,531

3,134

10

17,520

72

1,531

3,119

11

19,696