Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 41

Chapter 3: Parameter Settings

3–15

DDR or DDR2 SDRAM Controller with ALTMEMPHY Parameter Settings

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

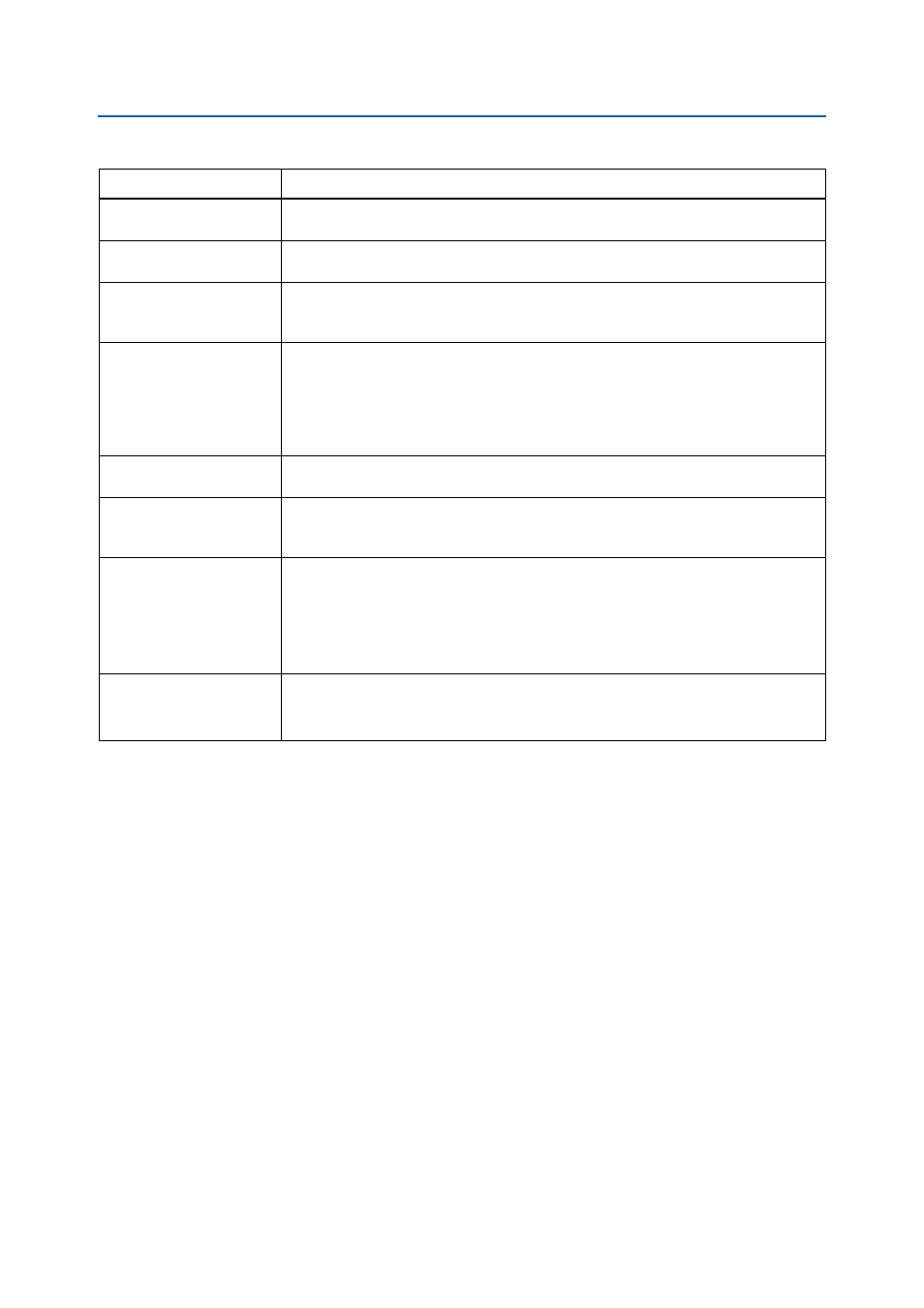

Command queue look-ahead

depth

Specifies a command queue look-ahead depth value to control the number of read or write

requests the look-ahead bank management logic examines.

Local maximum burst count

Specifies a burst count to configure the maximum Avalon burst count that the controller

slave port accepts.

Reduce controller latency by

Specifies, in controller clock cycles, a value by which to reduce the controller latency. The

default value is 0 but you have the option to choose 1 to enhance the latency performance of

your design at the expense of timing closure.

Enable configuration and

status register interface

Turn on to enable run-time configuration and status retrieval of the memory controller.

Enabling this option adds an additional Avalon-MM slave port to the memory controller top

level that allows run-time reconfiguration and status retrieving for memory timing

parameters, memory address size and mode register settings, and controller features. If the

Error Detection and Correction Logic option is enabled, the same slave port also allows you

to control and retrieve the status of this logic. Refer to

Enable error detection and

correction logic

Turn on to enable error correction coding (ECC) for single-bit error correction and double-bit

error detection.

Enable auto error correction

Turn on to allow the controller to perform auto correction when the ECC logic detects a

single-bit error. Alternatively, you can turn off this option and schedule the error correction

at a desired time for better system efficiency.

Multiple controller clock

sharing

This option is only available in SOPC Builder Flow. Turn on to allow one controller to use the

Avalon clock from another controller in the system that has a compatible PLL. This option

allows you to create SOPC Builder systems that have two or more memory controllers that

are synchronous to your master logic.

1

This option is not for use with Cyclone III or Cyclone IV family devices.

Local interface protocol

Specifies the local side interface between the user logic and the memory controller. The

Avalon-MM interface allows you to easily connect to other Avalon-MM peripherals.

The HPC II architecture supports only the Avalon-MM interface.

Table 3–8. Controller Settings (Part 2 of 2)

Parameter

Description