Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 54

5–8

Chapter 5: Functional Description—ALTMEMPHY

Block Description

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

For full-rate clock and reset management refer to

Table 5–4

. The PLL is configured

exactly in the same way as in half-rate designs. The PLL information and restriction

from half-rate designs also applies.

1

The phy_clk_1x clock is now full-rate, despite the “1x” naming convention.

You must choose a PLL and PLL input clock pin that are located on the same side of

the memory interface to ensure minimal jitter. Cascaded PLLs are not recommended

for DDR/DDR2 SDRAM interfaces as jitter can accumulate with the use of cascaded

PLLs causing the memory output clock to violate the memory device jitter

specification. Also, ensure that the input clock to the PLL is stable before the PLL

locks. If not, you must perform a manual PLL reset and relock the PLL to ensure that

the phase relationship between all PLL outputs are properly set. The PLL restrictions

in half-rate designs also applies to full-rate designs.

Half-rate

and full rate

ac_clk_2x

—

0,

90

,180

, 270

Full-Rate

Global

The ac_clk_2x clock is

derived from either

mem_clk_2x

(when you

choose 0

or 180 phase

shift) or write_clk_2x

(when you choose 90

or

270

phase shift). Refer

to

for illustrations

of the address and

command clock

relationship with the

mem_clk_2x

or

write_clk_2x

signals.

Notes to

Table 5–4

:

(1) In full-rate designs a _1x clock may run at full rate clock.

(2) This clock should be of the same clock network clock as the resync_clk_2x clock.

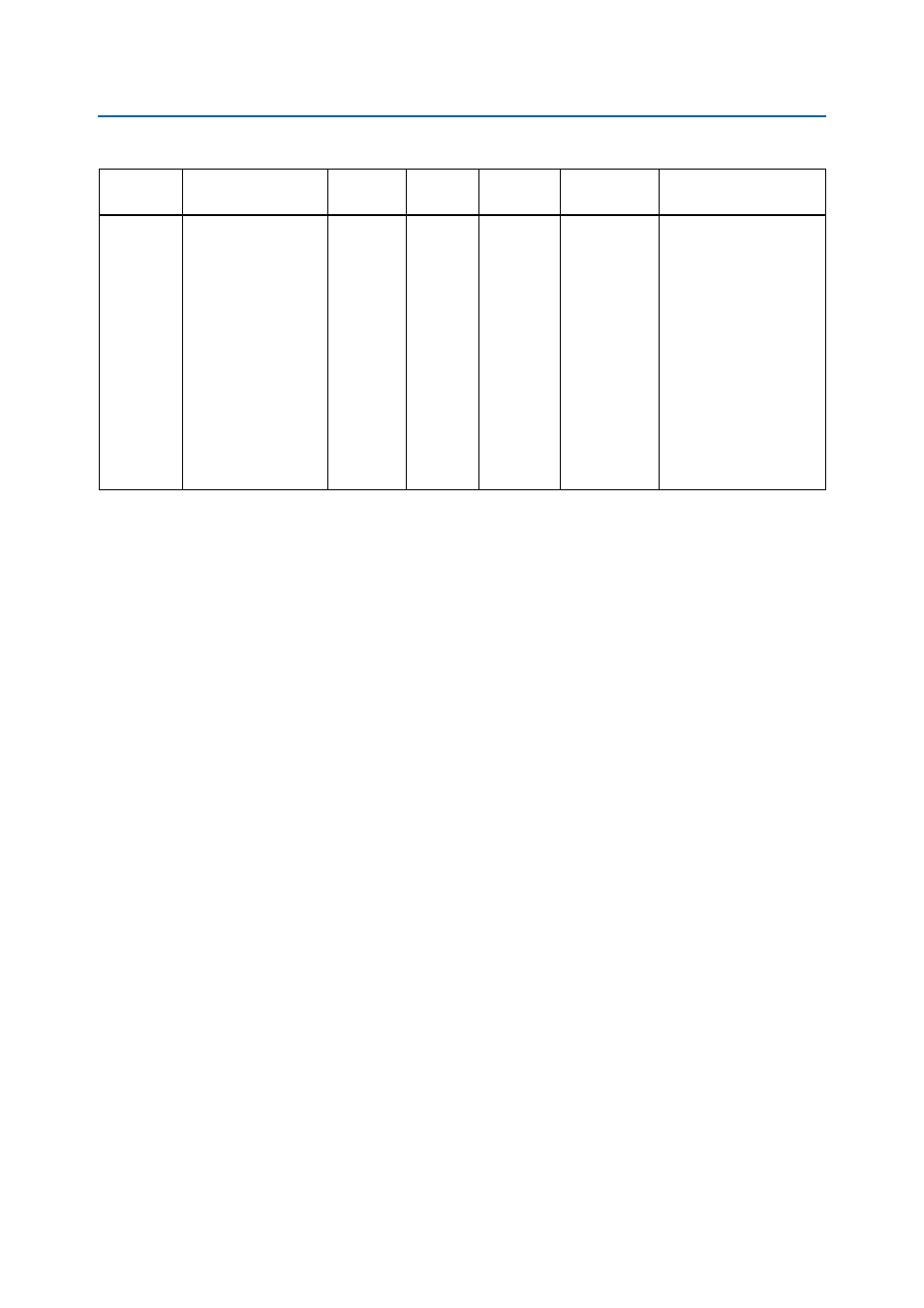

Table 5–1. DDR/DDR2 SDRAM Clocking in Arria GX, HardCopy II, Stratix II, and Stratix II GX Devices (Part 3 of 3)

Design

Rate

Clock Name

Postscale

Counter

Phase

(Degrees)

Clock Rate

Clock

Network Type

Notes