Example top-level file, Example top-level file –19 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 113

Chapter 6: Functional Description—High-Performance Controller II

6–19

Example Top-Level File

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Example Top-Level File

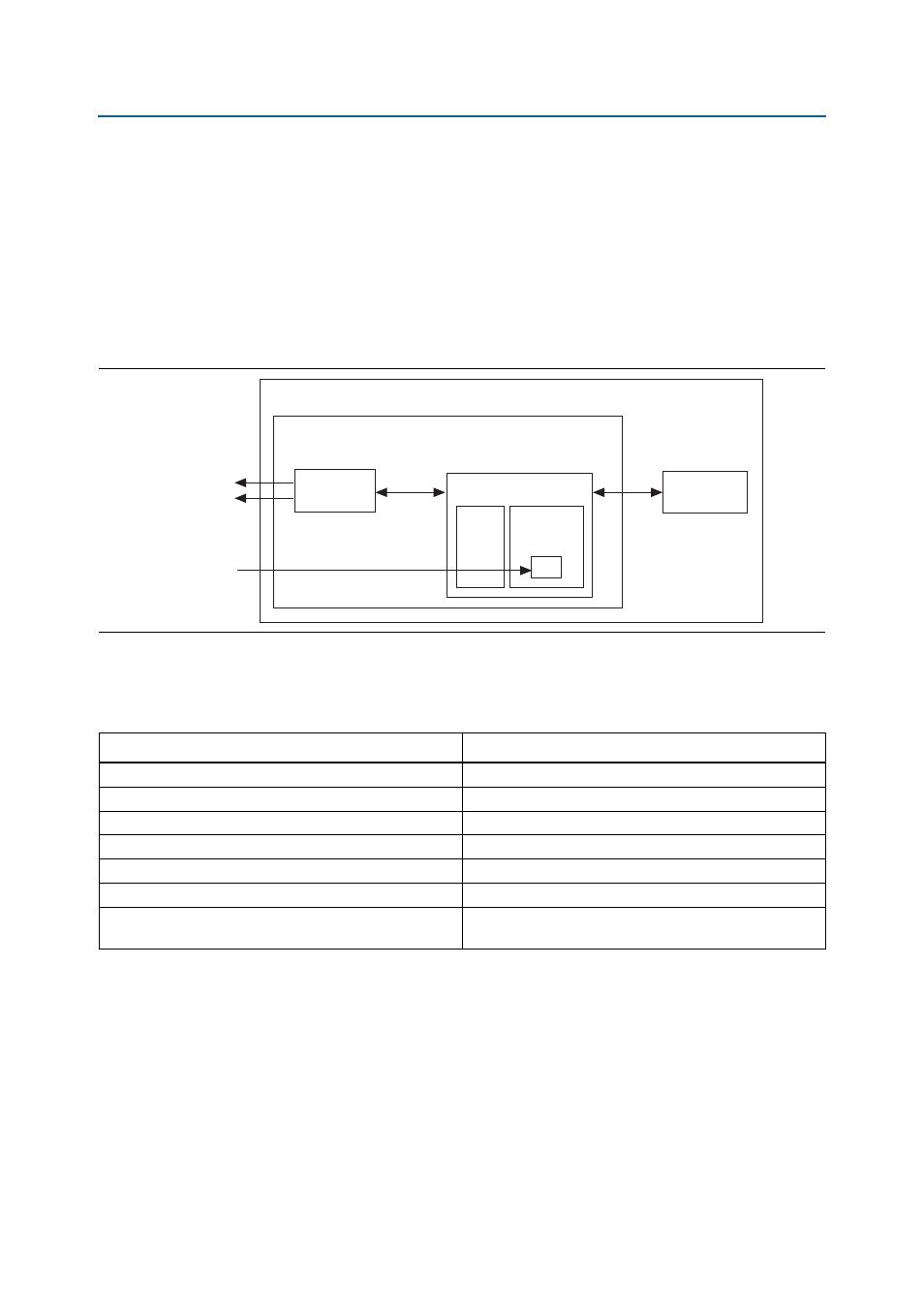

The MegaWizard Plug-In Manager helps you create an example top-level file that

shows you how to instantiate and connect the DDR or DDR2 SDRAM HPC II. The

example top-level file consists of the DDR or DDR2 SDRAM HPC II, some driver logic

to issue read and write requests to the controller, a PLL to create the necessary clocks,

and a DLL (Stratix series only). The example top-level file is a working system that

you can compile and use for both static timing checks and board tests.

Figure 6–6

shows the testbench and the example top-level file.

Table 6–10

describes the files that are associated with the example top-level file and

the testbench.

There are two Altera-generated memory models available—associative-array

memory model and full-array memory model.

The associative-array memory model (

reduced set of memory addresses with a default depth of 2,048 or 2K address spaces.

This allocation allows for a larger memory array compilation and simulation which

enables you to easily reconfigure the depth of the associate array.

The full-array memory model (

memory for all addresses accessible by the DDR cores. This allocation makes it

impossible to simulate large memory designs.

Figure 6–6. Testbench and Example Top-Level File

Example Driver

ALTMEMPHY

Control

Logic

clock_source

test_complete

pnf

Example Design

Testbench

DDR SDRAM Controller

Wizard-

Generated

Memory Model

DLL

PLL

Table 6–10. Example Top-Level File and Testbench Files

Filename

Description

Testbench for the example top-level file.

top-level

file.

Associative-array memory model.

Full-array memory model.

Example driver.

Top-level description of the custom MegaCore function.

Contains Quartus II project information for your MegaCore

function variations.