Sequence of operations, Write command, Sequence of operations –17 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 111: Write command –17

Chapter 6: Functional Description—High-Performance Controller II

6–17

Sequence of Operations

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Table 6–9

shows the CSR interface signals.

Sequence of Operations

This section explains how the various blocks pass information in common situations.

Write Command

When a requesting master issues a write command together with write data, the

following events occur:

■

The input interface accepts the write command and the write data.

■

The input interface passes the write command to the command generator and the

write data to the write data buffer.

■

The command generator processes the command and sends it to the timing bank

pool.

■

Once all timing requirements are met and a write-data-ready notification has been

received from the write data buffer, the timing bank pool sends the command to

the arbiter.

■

When rank timing requirements are met, the arbiter grants the command request

from the timing bank pool and passes the write command to the AFI interface.

mem_err_out_n

(1)

Input

Signal sent from the DIMM to the PHY to indicate that a parity error has

occured for a particular cycle. DDR3 SDRAM only.

Notes to

Table 6–8

:

(1) This signal is for registered DIMMs only.

Table 6–8. Interface Signals (Part 2 of 2)

Signal Name

Direction

Description

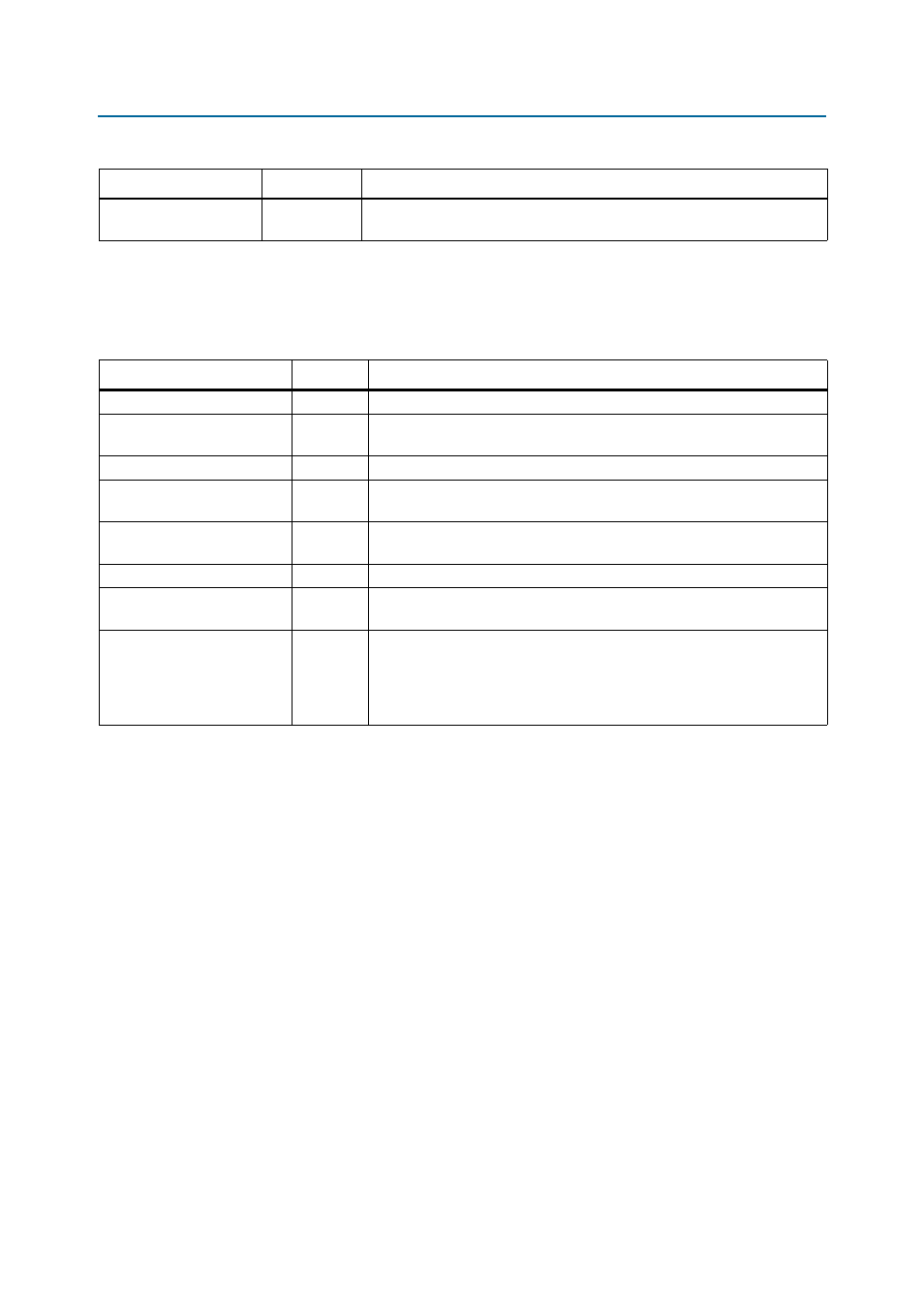

Table 6–9. CSR Interface Signals

Signal Name

Direction

Description

csr_addr[]

Input

Register map address.The width of csr_addr is 16 bits.

csr_be[]

Input

Byte-enable signal, which you use to mask off individual bytes during writes.

csr_be

is active high.

csr_wdata[]

Input

Write data bus. The width of csr_wdata is 32 bits.

csr_write_req

Input

Write request signal. You cannot assert csr_write_req and csr_read_req

signals at the same time.

csr_read_req

Input

Read request signal. You cannot assert csr_read_req and

csr_write_req

signals at the same time.

csr_rdata[]

Output

Read data bus. The width of csr_rdata is 32 bits.

csr_rdata_valid

Output

Read data valid signal. The csr_rdata_valid signal indicates that valid data

is present on the read data bus.

csr_waitrequest

Output

The csr_waitrequest signal indicates that the HPC II is busy and not ready

to accept request signals. If the csr_waitrequest signal goes high in the

clock cycle when a read or write request is asserted, that request is not

accepted. If the csr_waitrequest signal goes low, the HPC II is then ready

to accept more requests.