Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 56

5–10

Chapter 5: Functional Description—ALTMEMPHY

Block Description

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Half-rate

and full

rate

write_clk_2x

C3

–90

Full-Rate

Global Regional

Clocks the data out of

the DDR I/O (DDIO)

pins in advance of the

DQS strobe (or

equivalent). As a result,

its phase leads that of

the mem_clk_2x by

90°.

Half-rate

and full

rate

ac_clk_2x

C3

90

Full-Rate

Global

Regional

Address and command

clock.

The ac_clk_2x clock is

derived from either

mem_clk_2x

(when you

choose 0

or 180

phase shift) or

write_clk_2x

(when

you choose 90

or

270

phase shift). Refer

for

illustrations of the

address and command

clock relationship with

the mem_clk_2x or

write_clk_2x

signals.

Half-rate

and full

rate

cs_n_clk_2x

C3

90

Full-Rate

Global

Global

Memory chip-select

clock.

The cs_n_clk_2x clock

is derived from

ac_clk_2x

.

Half-rate

and full

rate

resync_clk_2x

C4

Calibrated

Full-Rate

Global

Regional

Clocks the

resynchronization

registers after the

capture registers. Its

phase is adjusted to the

center of the data valid

window across all the

DQS-clocked DDIO

groups.

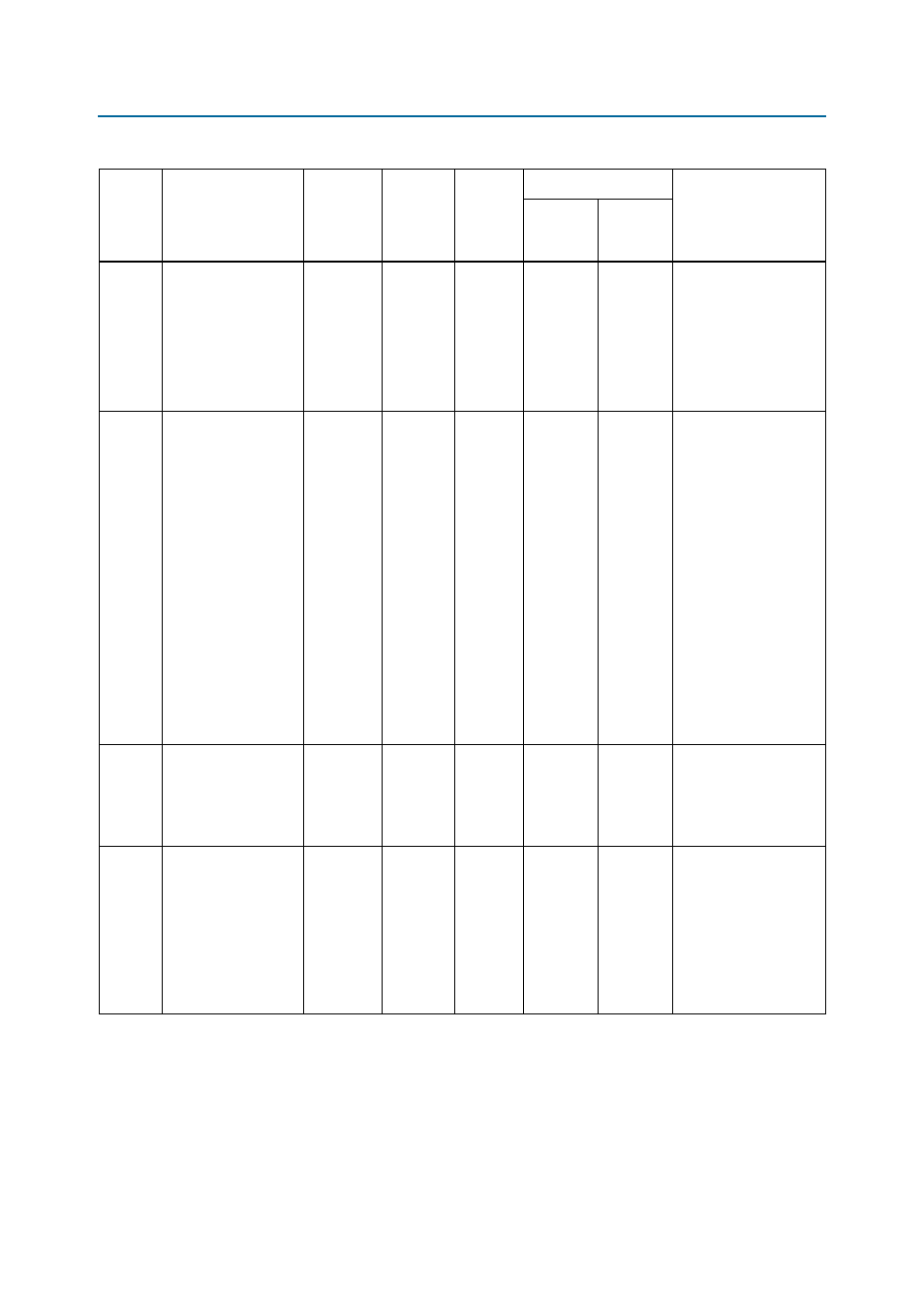

Table 5–2. DDR/DDR2 SDRAM Clocking in Arria II GX Devices (Part 2 of 3)

Design

Rate

Clock Name

(1)

Postscale

Counter

Phase

(Degrees)

Clock

Rate

Clock Network Type

Notes

All

Quadrants

Any 3

Quadrants

(2)