Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 55

Chapter 5: Functional Description—ALTMEMPHY

5–9

Block Description

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Table 5–2

shows the clock outputs that Arria II GX devices use.

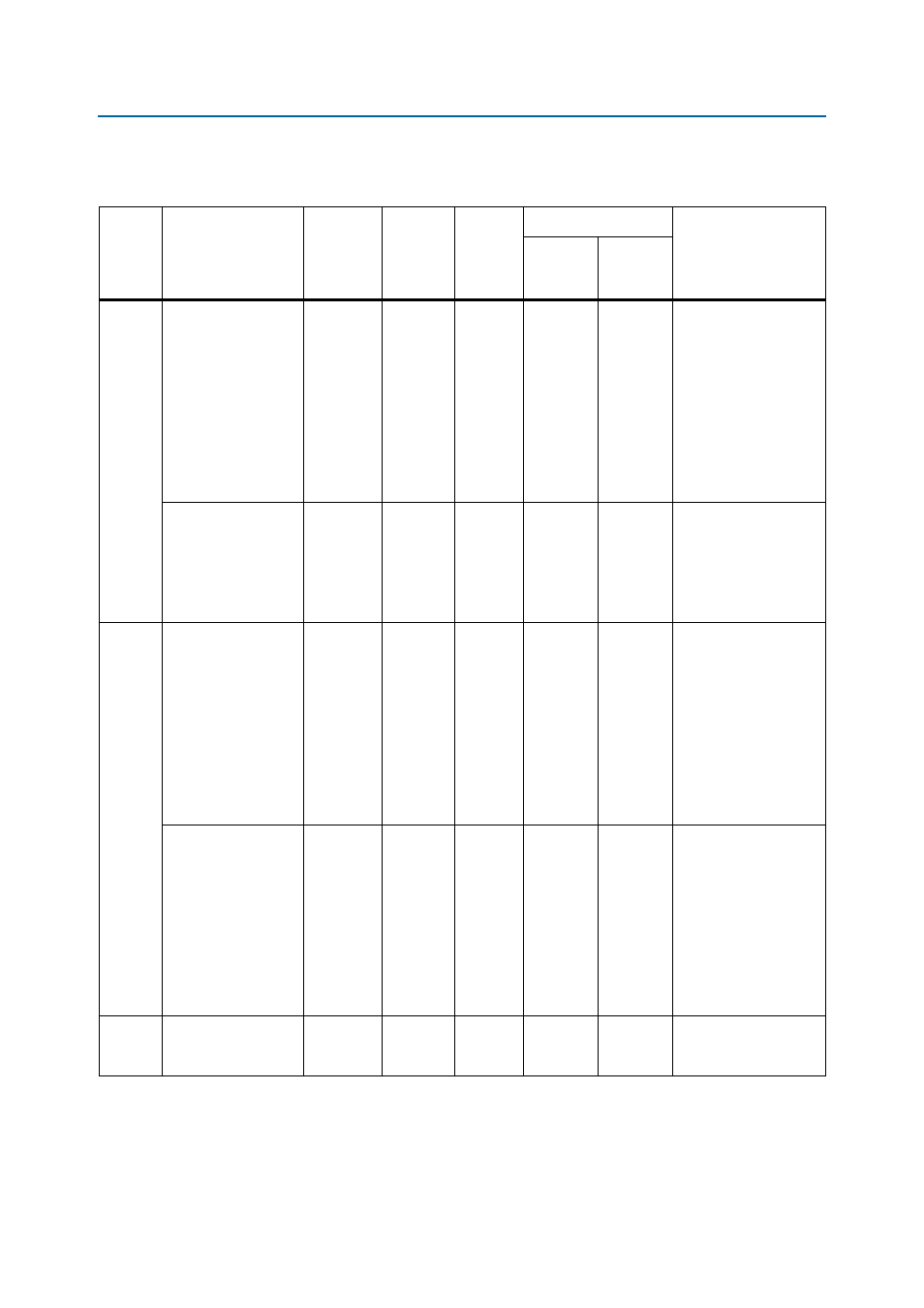

Table 5–2. DDR/DDR2 SDRAM Clocking in Arria II GX Devices (Part 1 of 3)

Design

Rate

Clock Name

(1)

Postscale

Counter

Phase

(Degrees)

Clock

Rate

Clock Network Type

Notes

All

Quadrants

Any 3

Quadrants

Half-rate

phy_clk_1x

and

aux_half_rate_clk

C0

0

Half-Rate

Global

Global

The only clock

parameterizable for the

ALTMEMPHY

megafunction. This

clock also feeds into a

divider circuit to provide

the PLL scan_clk

signal (for

reconfiguration) that

must be lower than

100 MHz.

mem_clk_2x

and

aux_full_

rate_clk

C1

0

Full-Rate

Global

Regional

Clocks DQS and as a

reference clock for the

memory devices.

Full rate

aux_half_rate_clk

C0

0

Half-Rate

Global

Global

The only clock

parameterizable for the

ALTMEMPHY

megafunction. This

clock also feeds into a

divider circuit to provide

the PLL scan_clk

signal (for

reconfiguration) that

must be lower than

100 MHz.

phy_clk_1x

(1)

and

mem_clk_2x

and

aux_full_

rate_clk

C1

0

Full-Rate

Global

Regional

Clocks DQS and as a

reference clock for the

memory devices.

Half-rate

and full

rate

Unused

C2

—

—

—

—

—