Stratix iii and stratix iv devices, Stratix iii and stratix iv devices –24 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 70

5–24

Chapter 5: Functional Description—ALTMEMPHY

Block Description

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Stratix III and Stratix IV Devices

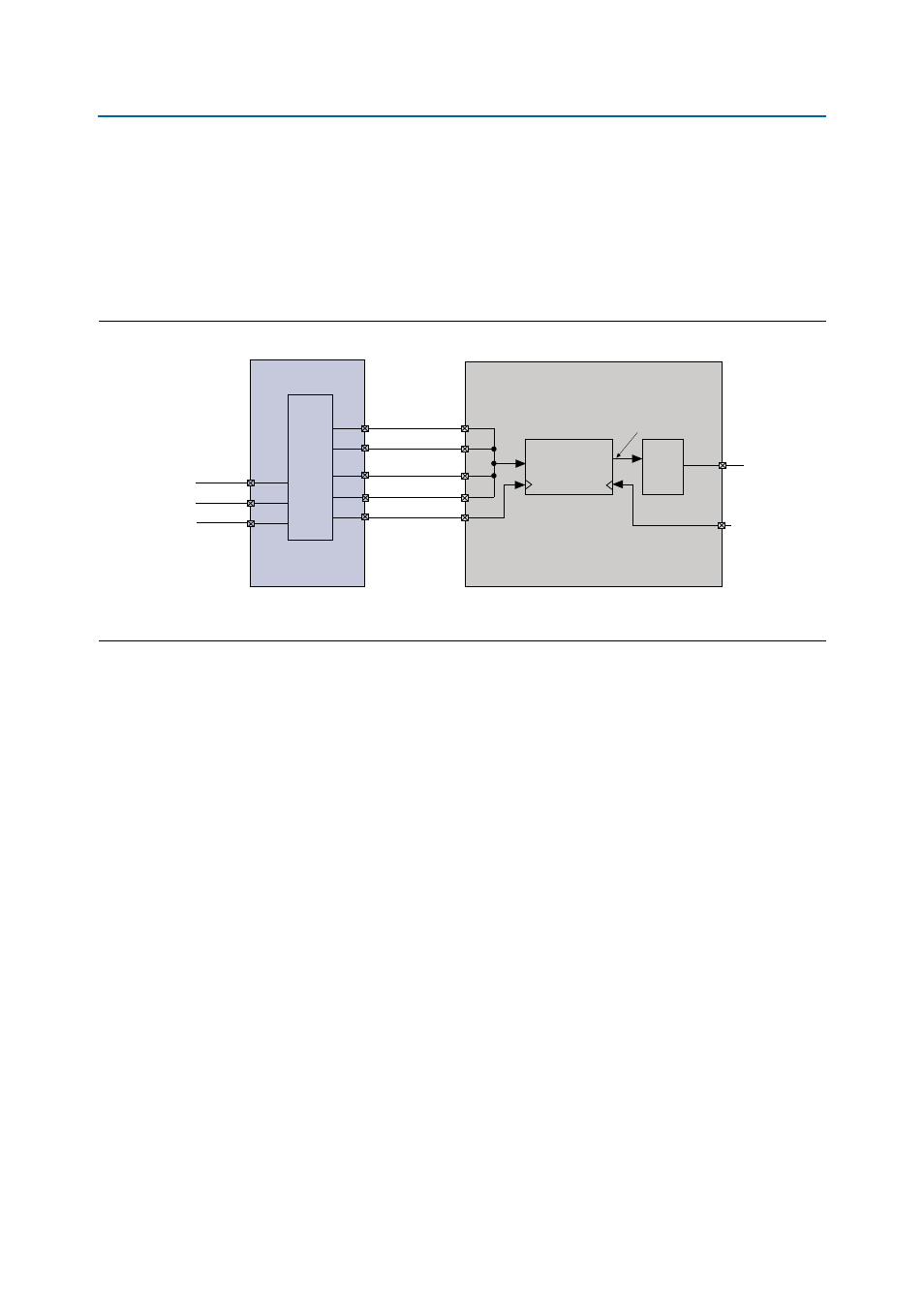

Stratix IV and Stratix III devices support half-rate or full-rate DDR/DDR2 SDRAM.

The Stratix IV and Stratix III read datapath (

Figure 5–8

) consists of two main blocks:

■

Data capture, resynchronization, and demultiplexing

■

Read datapath logic (read datapath)

Data Capture, Resynchronization, and Demultiplexing

In Stratix IV and Stratix III devices, the smart interface module in the IOE performs

the following tasks:

■

Captures the data

■

Resynchronizes the captured data from the DQS domain to the resynchronization

clock (resync_clk_1x) domain

■

Converts the resynchronized data into half-rate data, which is performed by

feeding the resynchronized data into the HDR conversion block within the IOE,

which is clocked by the half-rate version of the resynchronization clock. The

resync_clk_1x

signal is generated from the I/O clock divider module based on

the resync_clk_2x signal from the PLL.

f

For more information about IOE registers, refer to the

External Memory Interfaces in

Stratix III Devices

chapter in volume 1 of the Stratix III Device Handbook and the

chapter in volume 1 of the Stratix IV

Device Handbook.

Figure 5–8. DDR/DDR2 SDRAM Data Capture and Read Data Mapping in Stratix IV and Stratix III Devices

Note to

Figure 5–8

:

(1) This figure shows a half-rate variation. For a full-rate controller, dio_radata2_1x and dio_rdata3_1x are unconnected.

Dual Port RAM

Read Datapath

Data Capture, Resynchronization,

and Data Demultiplexing

mem_dq

dio_rdata3_1x

IOE

mem_dqs

mem_dqsn

dio_rdata2_1x

dio_rdata1_1x

dio_rdata0_1x

resync_clk_1x

4n bits

wr_data

wr_clk

rd_data

rd_clk

ctl_rdata

ram_rdata_1x[4n]

phy_clk_1x

Data

Mapping

Logic