Board settings, Board settings –12 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 38

3–12

Chapter 3: Parameter Settings

ALTMEMPHY Parameter Settings

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Board Settings

Click Next or the Board Settings tab to set the options described in

Table 3–7

. The

board settings parameters are set to model the board level effects in the timing

analysis. The options are available if you choose Arria II GX or Stratix IV device for

your interface. Otherwise, the options are disabled.

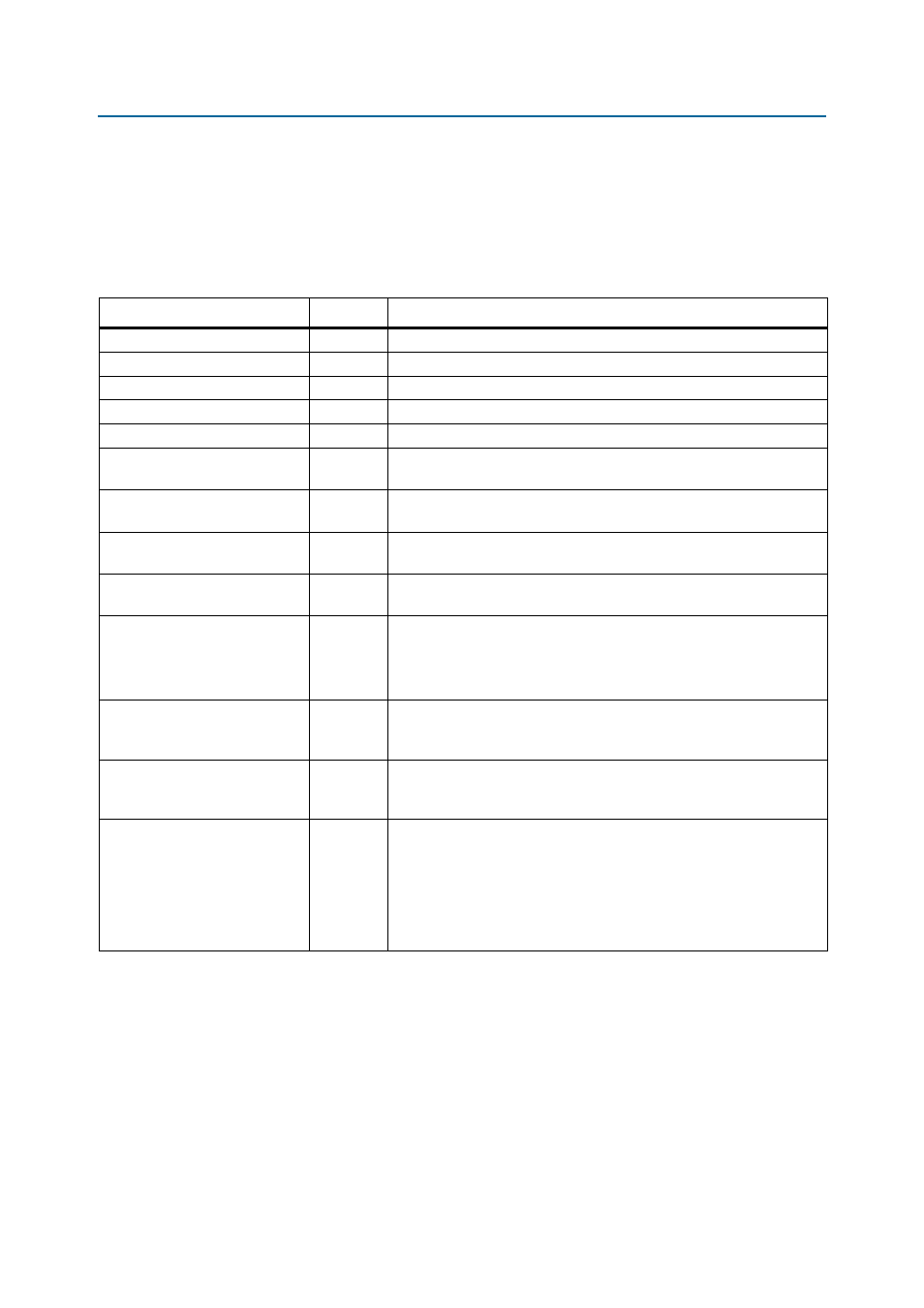

Table 3–7. ALTMEMPHY Board Settings

Parameter Name

Units

Description

Number of slots/discrete devices

—

Sets the single-rank or multi-rank configuration.

CK/CK# slew rate (differential)

V/ns

Sets the differential slew rate for the CK and CK# signals.

Addr/command slew rate

V/ns

Sets the slew rate for the address and command signals.

DQ/DQS# slew rate (differential)

V/ns

Sets the differential slew rate for the DQ and DQS# signals.

DQ slew rate

V/ns

Sets the slew rate for the DQ signals.

Addr/command eye reduction

(setup)

ns

Sets the reduction in the eye diagram on the setup side due to the ISI on

the address and command signals.

Addr/command eye reduction

(hold)

ns

Sets the reduction in the eye diagram on the hold side due to the ISI on

the address and command signals.

DQ eye reduction

ns

Sets the total reduction in the eye diagram on the setup side due to the ISI

on the DQ signals.

Delta DQS arrival time

ns

Sets the increase of variation on the range of arrival times of DQS due to

ISI.

Max skew between

DIMMs/devices

ns

Sets the largest skew or propagation delay on the DQ signals between

ranks, especially true for DIMMs in different slots.

This value affects the Resynchronization margin for the DDR2 interfaces

in multi-rank configurations for both DIMMs and devices.

Max skew within DQS group

ns

Sets the largest skew between the DQ pins in a DQS group. This value

affects the Read Capture and Write margins for the DDR2 interfaces in all

configurations (single- or multi-rank, DIMM or device).

Max skew between DQS groups

ns

Sets the largest skew between DQS signals in different DQS groups. This

value affects the Resynchronization margin for the DDR2 interfaces in

both single- or multi-rank configurations.

Addr/command to CK skew

ns

Sets the skew or propagation delay between the CK signal and the address

and command signals. The positive values represent the address and

command signals that are longer than the CK signals, and the negative

values represent the address and command signals that are shorter than

the CK signals. This skew is used by the Quartus II software to optimize

the delay of the address/command signals to have appropriate setup and

hold margins for the DDR2 interfaces.