Altmemphy signals, Altmemphy signals –27 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 73

Chapter 5: Functional Description—ALTMEMPHY

5–27

ALTMEMPHY Signals

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

1

For full-rate controllers, phy_clk_1x runs at full rate and there are only two bits of

wdata

.

The write datapath for full-rate PHYs is similar to the half-rate PHY. The IOE block is

identical to the half-rate PHY. The latency of the write datapath in the full-rate PHY is

less than in the half-rate PHY because the full-rate PHY does not have half-rate to

full-rate conversion logic.

f

For more information about the Stratix III I/O structure, re

in volume 1 of the Stratix III Device Handbook and

the

me 1 of the Stratix IV

Device Handbook.

ALTMEMPHY Signals

This section describes the ALMEMPHY megafunction ports for AFI variants.

Table 5–5

through

Table 5–7

show the signals.

1

Signals with the prefix mem_ connect the PHY with the memory device; signals with

the prefix ctl_ connect the PHY with the controller.

The signal lists include the following signal groups:

■

I/O interface to the SDRAM devices

■

Clocks and resets

■

External DLL signals

■

User-mode calibration OCT control

■

Write data interface

■

Read data interface

■

Address and command interface

■

Calibration control and status interface

■

Debug interface

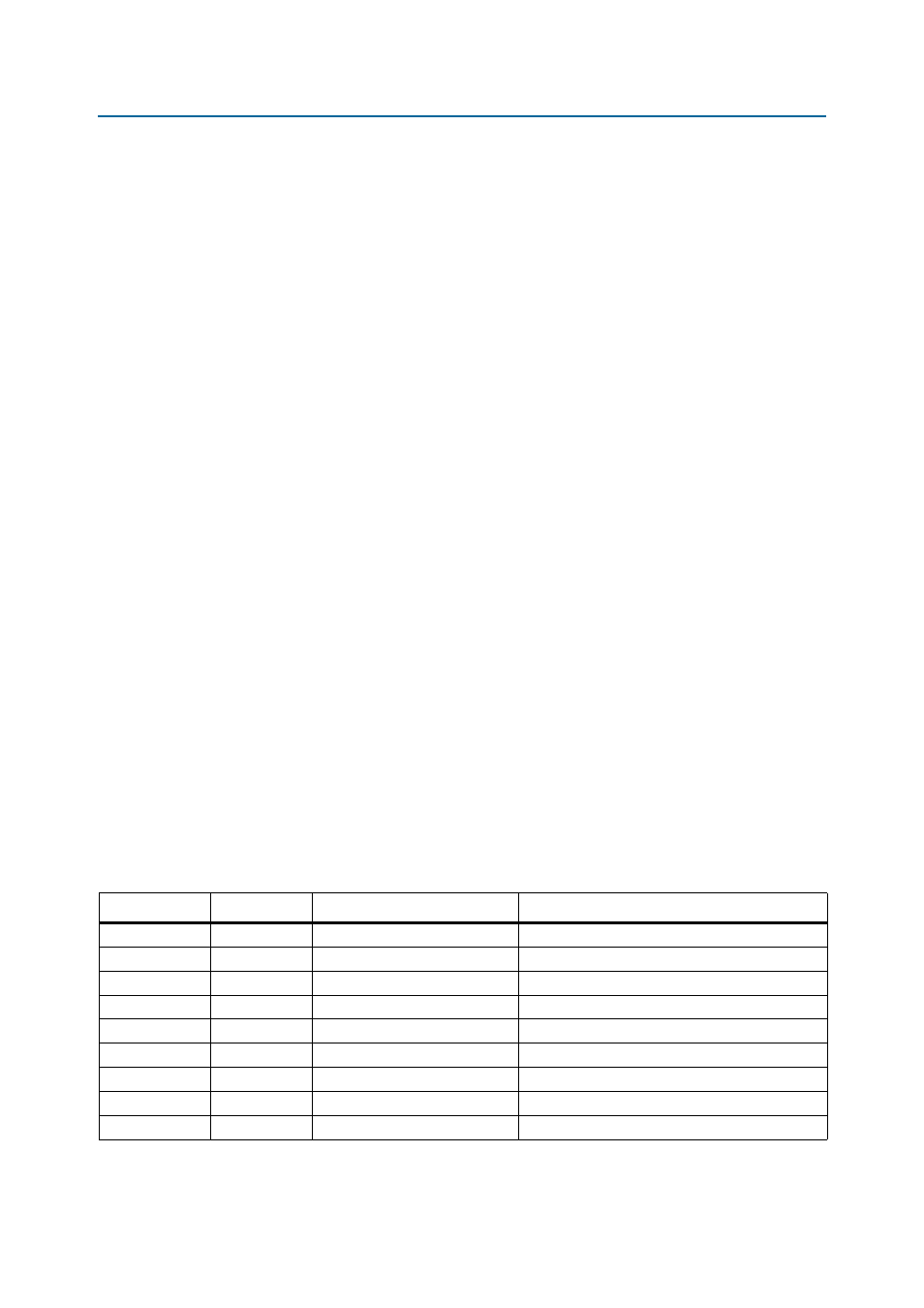

Table 5–5. Interface to the SDRAM Devices (Part 1 of 2)

(Note 1)

Signal Name

Type

Width

(2)

Description

mem_addr

Output

MEM_IF_ROWADDR_WIDTH

The memory row and column address bus.

mem_ba

Output

MEM_IF_BANKADDR_WIDTH

The memory bank address bus.

mem_cas_n

Output

1

The memory column address strobe.

mem_cke

Output

MEM_IF_CS_WIDTH

The memory clock enable.

mem_clk

Bidirectional

MEM_IF_CLK_PAIR_COUNT

The memory clock, positive edge clock.

(3)

mem_clk_n

Bidirectional

MEM_IF_CLK_PAIR_COUNT

The memory clock, negative edge clock.

mem_cs_n

Output

MEM_IF_CS_WIDTH

The memory chip select signal.

mem_dm

Output

MEM_IF_DM_WIDTH

The optional memory DM bus.

mem_dq

Bidirectional

MEM_IF_DWIDTH

The memory bidirectional data bus.