System requirements, System requirements –6, Table 1–6 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 12: Show typica

1–6

Chapter 1: About This IP

System Requirements

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

System Requirements

The DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP are part of the

MegaCore IP Library, which is distributed with the Quartus II software and

downloadable from the Altera

website,

Controller+PHY

DDR2

(Half rate)

8

2,737

5,131

6

4,784

16

2,915

5,351

9

9,392

64

3,969

6,564

27

37,040

72

4,143

6,786

28

41,648

DDR2

(Full rate)

8

2,418

4,763

6

2,576

16

2,499

4,919

6

5,008

64

2,957

5,505

15

19,600

72

3,034

5,608

16

22,032

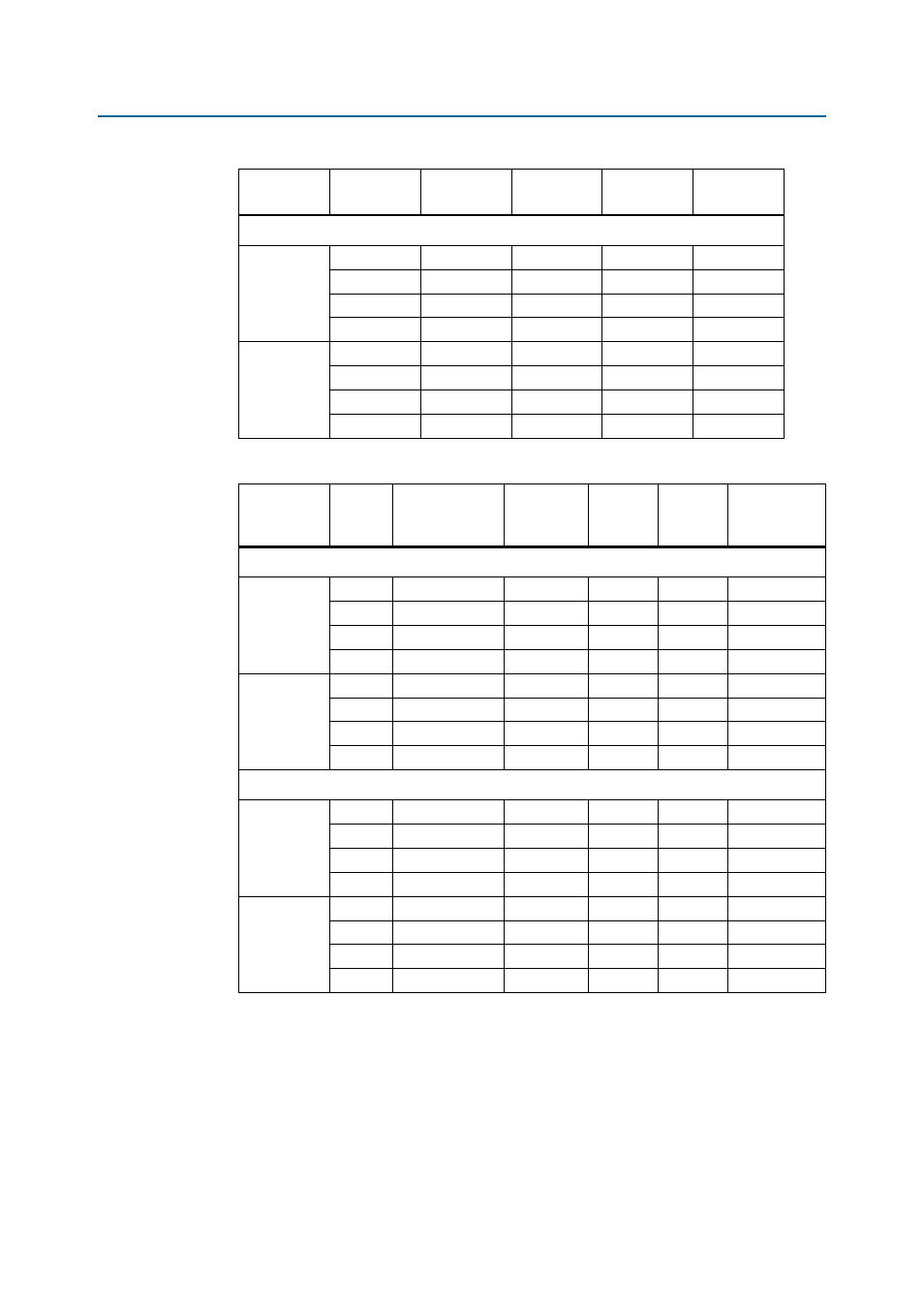

Table 1–6. DDR2 Resource Utilization in Stratix II Devices

Protocol

Memory

Width

(Bits)

Combinational

ALUTS

Logic

Registers

M4K

Blocks

M512

Blocks

Memory (Bits)

Controller

DDR2

(Half rate)

8

1,998

1,519

2

2

4,464

16

2,002

1,519

4

2

8,816

64

2,058

1,519

16

2

34,928

72

2,064

1,518

17

2

39,280

DDR2

(Full rate)

8

2,021

1,541

2

2

2,288

16

2,017

1,537

2

2

4,464

64

2,035

1,538

8

2

17,520

72

2,033

1,536

9

2

19,696

Controller+PHY

DDR2

(Half rate)

8

3,575

2,754

3

6

5,196

16

3,639

2,910

6

6

9,804

64

3,984

3,831

23

7

37,452

72

4,071

3,987

25

6

42,060

DDR2

(Full rate)

8

3,387

2,496

2

7

2,988

16

3,400

2,553

4

5

5,420

64

3,472

2,880

13

5

20,012

72

3,491

2,935

14

5

22,444

Table 1–5. DDR2 Resource Utilization in Cyclone III Devices (Part 2 of 2)

Protocol

Memory

Width (Bits)

Logic

Registers

Logic Cells

M9K Blocks

Memory

(Bits)